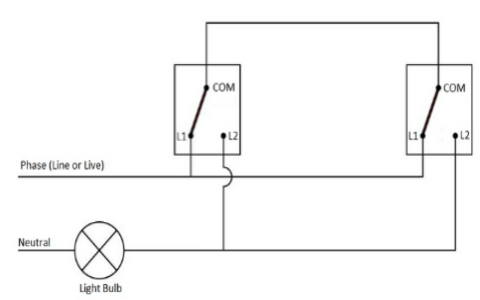

の主な欠点 組み合わせ回路 つまり、現在および以前の状態を保存するためにメモリを使用しません。したがって、以前の入力状態は回路の現在の状態に影響を与えません。一方、順序回路にはメモリがあるため、出力は入力に基づいて変化する可能性があります。このタイプの回路は、以前の入力、出力、クロック、およびメモリ要素を使用します。ここで、メモリ要素はラッチまたはフリップフロップにすることができます。シーケンシャル回路は、ROMやフリップ、PLA、 CPLD(Complex Programmable Logic Device) 、 FPGA(フィールドプログラマブルゲートアレイ) 。この記事では、PLAを使用して順序回路を設計する方法についてのみ説明します。

以下に示す順序回路のブロック図:

順序回路のブロック図

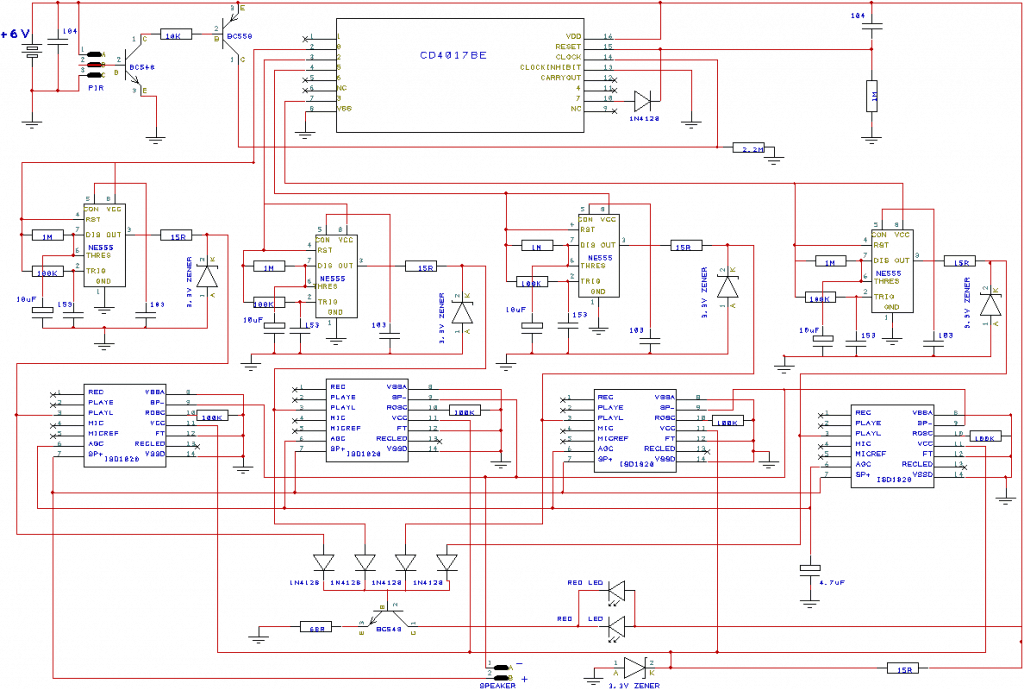

PLAを使用した順序回路の設計

順序回路 PLA(プログラマブルロジックアレイ)とフリップフロップを使用して実現できます。この設計では、状態の割り当てが重要になる場合があります。これは、適切な状態の割り当てを使用すると、必要な製品用語の数が減り、PLAの必要なサイズが減る可能性があるためです。リテラルの接続詞として定義される積項。各リテラルは変数またはその否定のいずれかです。

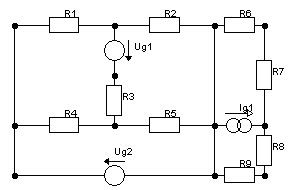

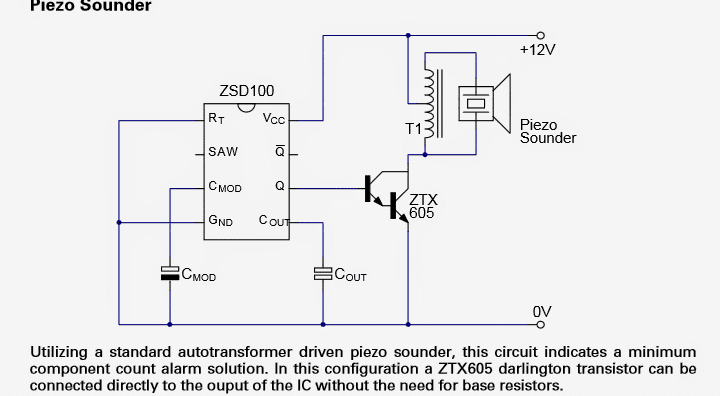

コードコンバーターの設計について考えてみましょう。以下の表に示す状態テーブルは、1つのPLAと3つのPLAを使用して実現できます。 ビーチサンダル 下図のように。この回路構成は、ROMが適切なサイズのPLAに置き換えられていることを除いて、ROMフリップフロップベースの設計と非常によく似ています。状態の割り当ては、以下に示す真理値表につながります。このテーブルは、4つの入力、13の積項、および4つの出力を備えたPLAに格納できますが、16ワードのROMと比較してサイズがほとんど小さくなりません。

| X Q1 Q2 Q3 | D1付きD2D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

表:真理値表

現在 状態

| 次の状態 X = 0 1 | 現在 出力(Z) |

| に | B C | 1 0 |

B C | D E そしてE | 1 0 0 1 |

D IS | H H H M | 0 1 1 0 |

H M | A A TO- | 0 1 1- |

テーブル:状態テーブル

PLAを使用した順序回路の設計

カルノー図から導出された入出力方程式

ここでは、7つの状態があるため、3つのDフリップフロップが必要です。したがって、4つの入力と4つの出力を備えたPLA回路が必要です。コードコンバーターの状態割り当てを考慮すると、結果の出力式とカルノーから導出されたDフリップフロップ入力式は次の式で記述できます。

D1 = Q1 + = Q2”

D2 = Q2 + = Q2”

D3 = Q3 + = Q1 Q2 Q3 = X” Q1 Q3” = X Q1” Q2”

Z = X” Q3” + X Q3

| X Q1 Q2 Q3 | D1付きD2D3 |

--- 0- -1 ----- --1 1 1 0 1-0 1 00- 0 --- 0 十一

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

これらの方程式に対応するPLA表は、上の表に示されています。この表は、4つの入力、7つの積項、および4つの出力を持つPLAを使用して実現できます。上記の設計の動作を最初に検証するために、X = 0およびQ1Q2Q3 = 000と仮定します。これにより、テーブル内の行– –0-および0– – -0が選択されるため、Z = 0およびD1D2D3 = 100になります。アクティブなクロックエッジの後、Q1Q2Q3 = 100。次の入力がX = 1の場合、行– – 0 –および– 1- –が選択されるため、Z = 0およびD1D2D3 = 110になります。アクティブなクロックエッジの後、Q1Q2Q3 = 110。

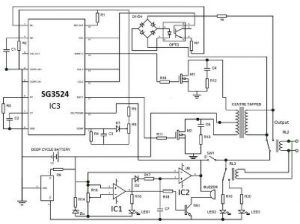

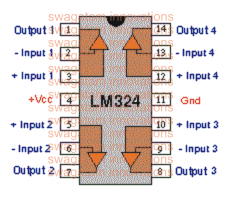

プログラマブルロジックアレイ(PLA)

プログラマブルロジックアレイは、プログラマブル論理デバイスです。これは通常、組み合わせ論理回路を実装するために使用されます。 PLAにはプログラム可能なANDプレーン(ANDアレイ)のセットがあり、プログラム可能なORプレーン(ORアレイ)のセットにリンクします。これらは暫定的に補完して出力を生成できます。このレイアウトにより、多数の論理関数を合成することができます。 製品の合計(SOP) 正規形。 PLAの簡単なブロック図を以下に示します。

PLAのブロック図

PLAとPAL(プログラマブルアレイロジック)の主な違いは、

PLA:両方 AND平面とOR平面 プログラム可能です。

PAL:ANDプレーンのみがプログラム可能で、ORプレーンは固定されています。

PLAをよりよく理解するために、ここでは以下の例を検討しています。

これらの関数f1とf2を実装してみましょう。

入力x1、x2、x3およびそれらのそれぞれの補完された信号はプログラム可能なANDプレーンに与えられ、そこで最小項と呼ばれるP1、P2、P3としてANDプレーン出力を取得します。次に、これらの信号がプログラム可能なORプレーンに与えられ、必要な出力関数f1およびf2(積の合計)が生成されます。次の図は、特定の機能に対するPLAのゲートレベルの実装を示しています。

人民解放軍の実施

これはすべて、PLAを使用した順序回路の設計に関するものです。この記事に記載されている情報は、この概念をよりよく理解するのに役立つと考えています。さらに、この記事に関する質問やヘルプ 電気および電子プロジェクトの実施 、下のコメントセクションにコメントすることで私たちにアプローチすることができます。ここにあなたへの質問があります、 順序回路とはどういう意味ですか?