ECL (エミッター結合ロジック) は、1956 年 8 月に IBM で Hannon S. Yourke によって最初に発明されました。このロジックは、電流モード ロジックとも呼ばれ、IBM 7090 & 7094 のコンピューターで使用されています。ECL ファミリーは、 デジタルロジック 家族。通常、このロジック ファミリの伝搬遅延は 1 ns 未満です。バイポーラ接合トランジスタに基づくロジックファミリーです。これは、従来のロジック システムを設計するためにアクセスできる最速のロジック ファミリ回路です。この記事では、 エミッタ結合論理回路 、アプリケーションの操作。

エミッタ結合ロジックとは

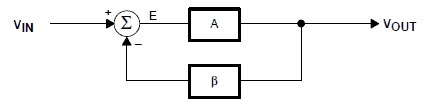

エミッタ結合ロジックが最適 BJT 従来のロジック システム設計で使用されるベースのロジック ファミリ。非常に高速なデジタル技術であるカレントモードロジックと呼ばれることもあります。一般に、ECLは、非常に小さな電圧スイングを使用し、トランジスタが飽和領域に入るのを回避することで高速動作を実現する最速のロジックICと見なされています。

ECL の実装では、PECL または正基準 ECL として知られる正の電源電圧を利用します。初期の ECL ゲートでは、ノイズ耐性のために負電圧供給が使用されます。その後、正基準 ECL は、TTL ロジック ファミリと比較してロジック レベルの互換性が高いため、非常に有名になりました。

エミッタ結合ロジックは大量の静的電力を消費しますが、全体的な電流消費は CMOS 高周波で。そのため、ECL は主にクロック分配回路と高周波ベースのアプリケーションで有益です。

エミッタ結合ロジック機能

ECL の機能により、多くの高性能ベースのアプリケーションで使用されるようになります。

- ECL は、回路の動作が差動増幅器に基づいているため、常に互いに補完する 2 つの出力を提供します。

- このロジック ファミリは、ロジック レベルが抵抗比の関数であるため、主にモノリシック製造方法に適しています。

- ECL ファミリのデバイスは、外部インバータを使用せずに、提案された機能の適切な相補出力を生成します。その結果、パッケージ数が減少し、電力の要件が減少し、時間の遅延から発生する問題も減少します。

- 差動アンプ設計の ECL デバイスは幅広い性能の柔軟性を提供するため、ECL 回路はデジタル回路とリニア回路の両方として使用できます。

- ECL ゲートの設計は、通常、高低の入力インピーダンスを持ち、大きなファンアウトと駆動能力を達成するのに非常に役立ちます。

- ECL デバイスは、電源の設計を簡素化するために、電源に一定の電流ドレインを生成します。

- オープン エミッタ出力を含む ECL のデバイスは、単純に伝送ライン ドライブ容量を含めることができます。

エミッタ結合論理回路

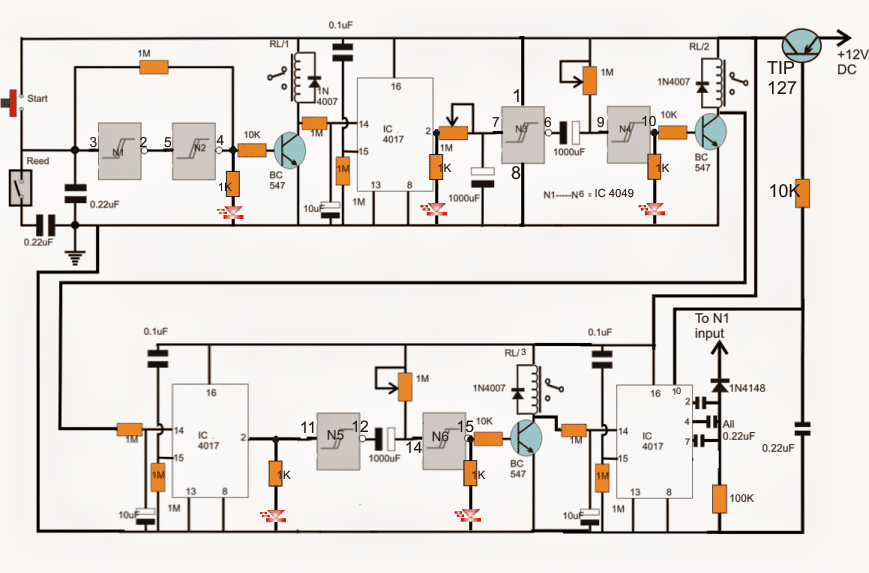

抵抗とトランジスタで設計されたインバータのエミッタ結合論理回路を以下に示します。この回路では、2 つのトランジスタのエミッタ端子は、トランジスタが飽和状態になるのを防ぐために使用される電流制限抵抗 RE に接続されているだけです。ここで、トランジスタの出力は、エミッタ端子ではなくコレクタ端子から取られます。この回路は、Vout (反転出力) と Vout2 (非反転出力) の 2 つの出力と、ハイまたはロー入力が与えられる Vin のような入力端子を提供します。 +Vcc = 5V。

エミッタ結合ロジックはどのように機能しますか?

エミッタ結合ロジックの動作は、HIGH 入力が ECL 回路に与えられるたびに、「Q1」トランジスタをオンにし、Q2 トランジスタをオフにしますが、Q1 トランジスタは飽和しません。したがって、これにより VOUT2 出力が HIGH にプルされ、VOUT1 出力の値は R1 内の降下により LOW になります。

同様に、ECL に与えられる VIN 値が LOW の場合、Q1 トランジスタがオフになり、Q2 トランジスタがオンになります。そのため、Q2 トランジスタは飽和状態にはなりません。したがって、VOUT1 出力が HIGH 値に引き上げられ、VOUT2 出力値は R2 抵抗内の降下により低くなります。

電圧が印加されたときにトランジスタ Q1 と Q2 がどのようにオン/オフするかを見てみましょう。

この回路のQ1とQ2のような2つのトランジスタは、共通のエミッタ抵抗によって差動増幅器として接続されています。

この回路例の電圧供給は、VCC = 5.0、VBB = 4.0 & VEE = 0 V です。入力 HIGH および LOW レベルの値は、単純に 4.4 V & 3.6 V と定義されています。実際、この回路は 0.6 ボルト高い LOW 出力と HIGH レベルを生成します。ただし、これは実際の ECL 回路内で修正されます。

Vin が HIGH になると、Q1 トランジスタがオンになりますが、飽和せず、Q2 トランジスタはオフになります。したがって、VOUT2 のような出力電圧は R2 抵抗を介して 5 V に引き下げられ、R1 抵抗の両端の電圧降下が約 0.8 V であるため、VOUT1 = 4.2 V (LOW) であることがわかります。さらに、トランジスタ Q1 が完全にオンになるため、VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V となります。

Vin が LOW になると、Q2 トランジスタはオンになりますが、飽和せず、Q1 トランジスタはオフになります。したがって、VOUT1 は R1 抵抗を使用して 5.0 V にプルされ、VOUT2 が 4.2 V であることを示すことができます。また、VE => VOUT2 – VQ2 => 4.2V – 0.8V => 3.4V で、トランジスタ Q2 がオンになります。

ECL では、t として 2 つのトランジスタが飽和することはありません。 入力/出力電圧のスイングは0.8vとかなり小さい 入力インピーダンスが高く、出力抵抗が低い。これにより、ECL はより少ない伝播遅延時間でより高速に動作することができます。

2 入力エミッタ結合ロジック OR/NOR ゲート回路

2 入力エミッタ結合論理 OR/NOR ゲート回路を以下に示します。この回路は上記のインバータ回路を改造したものです。変更は、入力側に余分なトランジスタを追加することです。

この回路の動作は非常に簡単です。 Q1 および Q2 トランジスタの両方に入力が適用されると、出力 1 (Vout1) が HIGH 値になります。したがって、この Vout1 は NOR ゲートの出力に相当します。

同時に、Q3 トランジスタがオンになると、2 番目の出力 (Vout2) が HIGH になります。したがって、この Vou2 出力は OR ゲート出力に対応します。

同様に、Q1 と Q2 の両方のトランジスタ入力が HIGH の場合、Q1 と Q2 のトランジスタがオンになり、VOUT1 端子に Low の出力が供給されます。

この動作中に Q3 トランジスタがオフになると、VOUT2 端子で高出力が提供されます。そのため、OR/NOR ゲートの真理値表を以下に示します。

|

入力 |

入力 | また |

または |

|

あ |

B | よ | よ |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

エミッタ結合ロジック特性

ECLの特徴としては、以下のようなものがあります。

- TTL と比較して、ECL は伝播時間が 0.5 ~ 2 ns と高速です。ただし、エミッタ結合ロジックの消費電力は、TTL に比べて 30 mW と高くなります。

- ECL の I/O 電圧は 0.8 のように小さなスイングを持っています。

- ECL の入力インピーダンスは高く、出力抵抗は低くなります。その結果、トランジスタはその状態を非常に速く変化させます。

- ECL のファンアウト容量は高く、ゲート遅延は低くなります。

- ECL の o/p ロジックは LOW から HIGH 状態に変化しますが、これらの状態の電圧レベルは TTL と EC の間で異なります。

- ECL のノイズ耐性は 0.4V です。

長所と短所

の エミッタ結合ロジックの利点 以下で説明します。

- ECL のファンアウトは 25 で、TTL に比べて優れており、CMOS に比べて低くなっています。

- ECL の平均伝播遅延時間は 1 ~ 4 ns であり、CMOS および

- TTL。したがって、それは最速のロジックファミリと呼ばれます。

- エミッターの BJT が結合されている場合 論理ゲート アクティブな領域で動作する場合、すべてのロジック ファミリと比較して最大速度になります。

- ECL ゲートは相補出力を生成します。

- 電源リード線に電流スイッチング スパイクはありません。

- 出力を結合して、ワイヤード OR 機能を提供できます。

- ECL のパラメータは、温度によってあまり変化しません。

- いいえ。オンリーチップからアクセスできる機能の割合が高い。

の エミッタ結合ロジックの欠点 以下で説明します。

- ノイズ マージンが非常に小さく、±200 mV です。

- 消費電力は、他の論理ゲートと比較して高いです。

- 他のロジック ファミリとインターフェイスするには、レベル シフターが必要です。

- ファンアウトは容量負荷を制限します。

- と比べて TTL 、ECLゲートは高価です。

- CMOS & TTL と比較すると、ECL ノイズ耐性は最悪です。

アプリケーション

エミッタ結合ロジックのアプリケーションには、次のものがあります。

- エミッタ結合ロジックは、光ファイバー トランシーバ インターフェイス、イーサネット、ATM (非同期転送モード) ネットワークなどの超高速通信デバイス内のロジックおよびインターフェイス テクノロジとして使用されます。

- ECL は BJT に基づくロジック ファミリであり、比較的小さな電圧スイングを使用し、トランジスタが飽和領域に移動するのを回避することによって高速動作を実現できます。

- ECL は、IBM 360/91 内で ASLT 回線を作成する際に使用されます。

- ECL は、シングルエンド バイアス i/p および一次トランジスタと二次トランジスタ間の正帰還を使用してインバータ機能を実現することにより、スタック トランジスタの使用を回避します。

- ECL は非常に高速な電子機器で使用されます。

したがって、これは エミッタ結合ロジックの概要 または ECL – 回路、動作、機能、特性、およびアプリケーション。 ECL は、他のデジタル ロジック ファミリと比較して、BJT に基づく非常に高速なロジック ファミリです。小さな電圧スイングを使用し、トランジスタが飽和領域に移動するのを回避することにより、最高速度の動作を実現します。このロジック ファミリは、信じられないほどの 1ns の伝播遅延を提供し、最新の ECL ファミリでは、この遅延が減少しています。ここで質問です。ECL の別名は何ですか?