CMOSという用語は「ComplementaryMetalOxideSemiconductor」の略です。これは、コンピュータチップ設計業界で最も人気のある技術の1つであり、今日、形成に広く使用されています。 集積回路 数多くのさまざまなアプリケーションで。今日のコンピュータメモリ、CPU、および携帯電話は、いくつかの重要な利点のためにこのテクノロジを利用しています。この技術は、PチャネルとNチャネルの両方の半導体デバイスを利用します。今日利用可能な最も人気のあるMOSFET技術の1つは、相補型MOSまたはCMOS技術です。これは、マイクロプロセッサ、マイクロコントローラチップ、RAM、ROMなどのメモリの主要な半導体技術です。 EEPROMと 特定用途向け集積回路(ASIC)。

MOSテクノロジー入門

IC設計では、基本的かつ最も重要なコンポーネントはトランジスタです。したがって、MOSFETは多くのアプリケーションで使用されるトランジスタの一種です。このトランジスタの形成は、半導体層、一般的にはウェーハ、シリコンの単結晶からのスライス、二酸化シリコンの層、および金属層を含めることによって、サンドイッチのように行うことができる。これらの層は、トランジスタが半導体材料内に形成されることを可能にする。 Sio2のような優れた絶縁体は、100分子の厚さの薄い層を持っています。

ゲート部に金属の代わりに多結晶シリコン(ポリ)を使用したトランジスタ。 FETのポリシリコンゲートは、大規模ICの金属ゲートをほぼ使用して置き換えることができます。ゲートの下のSio2は絶縁体であるため、ポリシリコンと金属FETの両方がIGFETと呼ばれることもあります。これは絶縁ゲートFETを意味します。

CMOS(相補型金属酸化膜半導体)

メイン MOSFETに対するNMOSの利点 BIPOLARテクノロジーは、はるかに小さい消費電力です。相補型MOS回路は、NMOSまたはBIPOLAR回路とは異なり、静的消費電力がほとんどありません。回路が実際に切り替わる場合にのみ、電力が消費されます。これにより、NMOSまたはNMOSよりも多くのCMOSゲートをICに統合できます。 バイポーラ技術 、結果としてパフォーマンスが大幅に向上します。相補型金属酸化膜半導体トランジスタは、PチャネルMOS(PMOS)とNチャネルMOS(NMOS)で構成されています。詳細については、リンクを参照してください CMOSトランジスタの製造プロセス 。

CMOS(相補型金属酸化膜半導体)

MOSFET

NMOSは、n型ソースとドレインが拡散したp型基板上に構築されています。 MOSFETでは、キャリアの大部分は電子です。ゲートに高電圧が印加されると、NMOSが導通します。同様に、ゲートに低電圧が印加されると、NMOSは導通しません。電子であるNMOSのキャリアは、正孔の2倍の速度で移動するため、NMOSはPMOSよりも高速であると見なされます。

MOSFETトランジスタ

MOSFET

PチャネルMOSFETは、N型基板上に拡散されたP型ソースとドレインで構成されています。キャリアの大部分は穴です。ゲートに高電圧が印加されると、PMOSは導通しません。ゲートに低電圧が印加されると、PMOSが導通します。 PBSデバイスは、NMOSデバイスよりもノイズの影響を受けません。

MOSFETトランジスタ

CMOS動作原理

CMOSテクノロジでは、N型トランジスタとP型トランジスタの両方を使用して論理関数を設計します。一方のタイプのトランジスタをオンにする同じ信号を使用して、もう一方のタイプのトランジスタをオフにします。この特性により、プルアップ抵抗を必要とせずに、単純なスイッチのみを使用してロジックデバイスを設計できます。

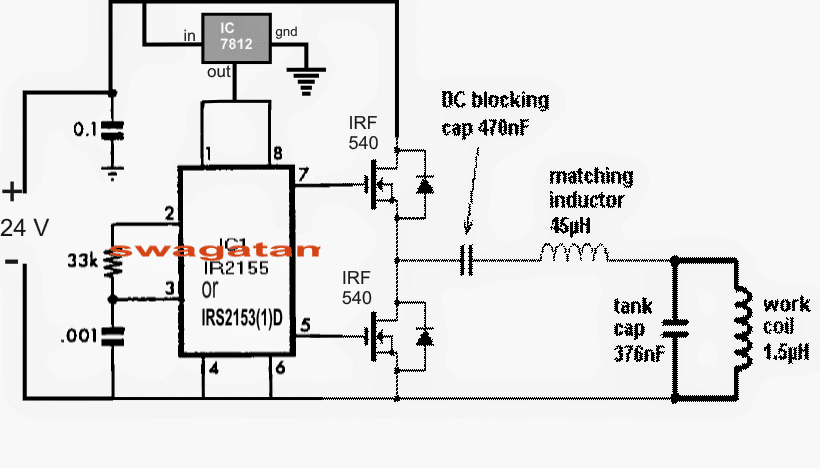

CMOSの場合 論理ゲート n型MOSFETのコレクションは、出力と低電圧電源レール(Vssまたは非常に多くの場合グランド)の間のプルダウンネットワークに配置されます。 CMOS論理ゲートは、NMOS論理ゲートの負荷抵抗の代わりに、出力と高電圧レール(Vddと呼ばれることが多い)の間のプルアップネットワークにp型MOSFETの集合を持っています。

プルアップ&プルダウンを使用したCMOS

したがって、p型トランジスタとn型トランジスタの両方のゲートが同じ入力に接続されている場合、n型MOSFETがオフのときにp型MOSFETがオンになり、その逆も同様です。ネットワークは、次の図に示すように、任意の入力パターンに対して一方がオンになり、もう一方がオフになるように配置されます。

CMOSは、両方の状態で比較的高速、低消費電力、高ノイズマージンを提供し、広範囲のソース電圧と入力電圧で動作します(ソース電圧が固定されている場合)。さらに、相補型金属酸化膜半導体の動作原理をよりよく理解するために、以下で説明するように、CMOS論理ゲートについて簡単に説明する必要があります。

どのデバイスがCMOSを使用していますか?

CMOSのような技術は、マイクロコントローラー、マイクロプロセッサー、SRAM(スタティックRAM)、その他のデジタル論理回路などのさまざまなチップで使用されています。この技術は、データコンバーター、イメージセンサー、数種類の通信用の高度に組み込まれたトランシーバーなど、幅広いアナログ回路で使用されています。

CMOSインバーター

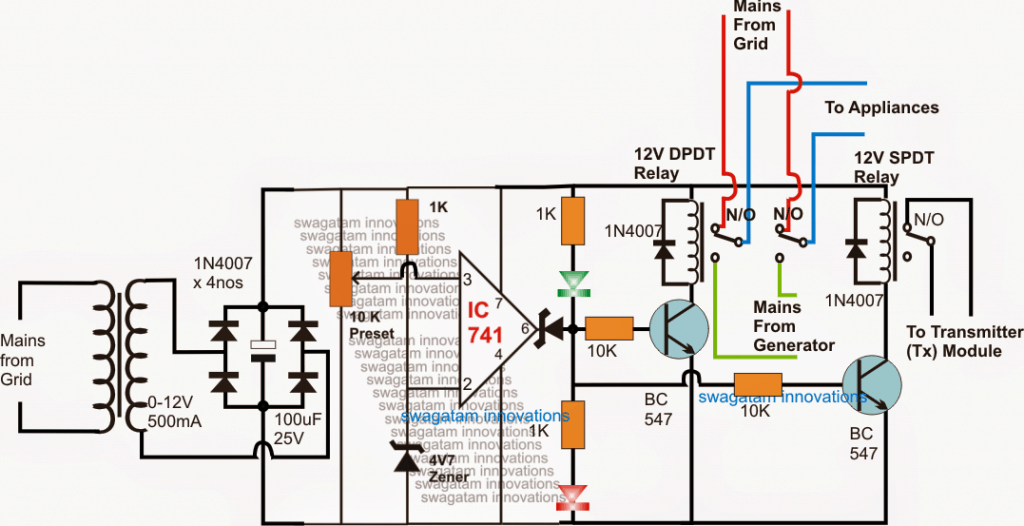

下図のようなインバータ回路。それはで構成されています PBSおよびNMOSFET 。入力Aは、両方のトランジスタのゲート電圧として機能します。

MOSFETトランジスタはVss(グランド)からの入力を持ち、PMOSトランジスタはVddからの入力を持っています。端子Yが出力されます。インバータの入力端子(A)に高電圧(〜Vdd)が印加されると、PMOSが開回路になり、NMOSがOFFになり、出力がVssにプルダウンされます。

CMOSインバーター

低レベル電圧の場合( 次の図は、2入力の相補型MOSNANDゲートを示しています。これは、Yとグラウンドの間の2つの直列NMOSトランジスタと、YとVDDの間の2つの並列PMOSトランジスタで構成されています。 入力AまたはBのいずれかがロジック0の場合、NMOSトランジスタの少なくとも1つがオフになり、Yからグランドへのパスが切断されます。ただし、pMOSトランジスタの少なくとも1つがオンになり、YからVDDへのパスが作成されます。 2入力NANDゲート したがって、出力Yは高くなります。両方の入力がハイの場合、両方のnMOSトランジスタがオンになり、両方のpMOSトランジスタがオフになります。したがって、出力はロジックローになります。以下の表に示すNAND論理ゲートの真理値表。 下図に2入力NORゲートを示します。どちらかの入力がハイの場合、NMOSトランジスタは並列になって出力をローに引き下げます。次の表に示すように、PMOSトランジスタは直列に接続されており、両方の入力がローのときに出力をハイにプルします。出力がフローティングのままになることはありません。 2入力NORゲート 以下の表に示すNOR論理ゲートの真理値表。 CMOSトランジスタの製造は、シリコンのウェーハ上で行うことができます。ウェーハの直径は20mmから300mmの範囲です。この点で、リソグラフィープロセスは印刷機と同じです。すべてのステップで、さまざまな材料を堆積させたり、エッチングしたり、パターン化したりすることができます。このプロセスは、単純化された組み立て方法でウェーハの上部と断面を表示することで非常に簡単に理解できます。 CMOSの製造は、Nウェルpt Pウェル、ツインウェル、SOI(Silicon on Insulator)の3つの技術を使用して実現できます。詳細については、このリンクを参照してください CMOS製作 。 CMOSバッテリーの一般的な寿命は約10年です。ただし、これは、PCがどこにある場合でも、使用率と環境に基づいて変化する可能性があります。 CMOSバッテリーに障害が発生すると、コンピューターの電源をオフにすると、コンピューターはコンピューターの正確な時刻と日付を維持できなくなります。たとえば、コンピュータの電源がオンになると、12:00PMや1990年1月1日のような日時が表示される場合があります。この障害は、CMOSのバッテリが故障していることを示しています。 CMOSの最も重要な特性は、低い静的電力使用率、大きなノイズ耐性です。 MOSFETトランジスタのペアからの単一のトランジスタがオフに切り替えられると、直列の組み合わせは、オンとオフのように述べられた2つの間の切り替え全体でかなりの電力を使用します。 その結果、これらのデバイスは、状態を変更しなくても通常は一定の定常電流を使用するTTLやNMOSロジックなどの他のタイプのロジック回路と比較して廃熱を生成しません。 これらのCMOS特性により、論理機能を高密度で集積回路に統合することができます。このため、CMOSはVLSIチップ内で実行される最も頻繁に使用される技術になりました。 MOSというフレーズは、半導体材料の酸化物絶縁体の上部に配置された金属ゲートを備えた電極を含むMOSFETの物理構造を指します。 アルミニウムのような材料は一度だけ使用されますが、材料は現在ポリシリコンです。他の金属ゲートの設計は、CMOSプロセスのプロセス内でのhigh-κ誘電体材料の到着によるカムバックを使用して行うことができます。 電荷結合デバイス(CCD)と相補型金属酸化膜半導体(CMOS)のようなイメージセンサーは、2つの異なる種類の技術です。これらは、画像をデジタルでキャプチャするために使用されます。すべてのイメージセンサーには、長所、短所、および用途があります。 CCDとCMOSの主な違いは、フレームのキャプチャ方法です。 CCDのような電荷結合デバイスはグローバルシャッターを使用しますが、CMOSはローリングシャッターを使用します。これらの2つのイメージセンサーは、電荷を光から電気に変化させ、電子信号に処理します。 CCDで使用される製造プロセスは、変更せずにIC全体で電荷を移動する能力を形成するために特別です。したがって、この製造プロセスは、光の感度と忠実度に関する非常に高品質のセンサーにつながる可能性があります。 対照的に、CMOSチップは固定製造手順を使用してチップを設計し、マイクロプロセッサの製造にも同様のプロセスを使用できます。製造上の違いにより、CCD 7CMOSのようなセンサー間には明らかな相違点がいくつかあります。 CCDセンサーはノイズが少なく高品質で画像をキャプチャしますが、CMOSセンサーは通常ノイズの影響を受けやすくなります。 通常、CMOSはより少ない電力を使用しますが、CCDはCMOSセンサーに対して100倍以上のように多くの電力を使用します。 CMOSチップの製造は、CCDと比較して非常に安価である傾向があるため、一般的なSi生産ラインで行うことができます。 CCDセンサーは、長期間大量生産されるため、より成熟しています。 CMOSイメージャとCCDイメージャはどちらも、光から電気信号を生成するために光電効果に依存しています 上記の違いに基づいて、CCDはカメラで使用され、多くのピクセルと卓越した光感度を通じて高品質の画像をターゲットにします。通常、CMOSセンサーの解像度、品質、感度は低くなります。 ラッチアップは、電源とアースなどの2つの端子間で短絡が発生し、大電流が発生してICが損傷する可能性がある場合と定義できます。 CMOSでは、ラッチアップは、寄生PNPとNPNのような2つのトランジスタ間の通信のために、電源レールと接地レールの間で低インピーダンスのトレイルが発生することです。 トランジスタ 。 CMOS回路では、PNPとNPNのような2つのトランジスタが、VDDとGNDのような2つの電源レールに接続されています。これらのトランジスタの保護は、抵抗を介して行うことができます。 ラッチアップ伝送では、電流は2つのトランジスタを介してVDDからGNDに直接流れるため、短絡が発生する可能性があります。したがって、極端な電流がVDDからグランド端子に流れます。 ラッチアップ防止にはさまざまな方法があります ラッチアップ防止では、次の方法を使用して、高抵抗をトレイルに配置して、電源全体の電流の流れを停止し、β1*β2を1未満にすることができます。 寄生SCRの構造は、PMOSやNMOSなどのトランジスタの周囲で絶縁酸化物層を介してビークされます。ラッチアップ保護のテクノロジーは、ラッチアップに気付くとデバイスの電源を切ります。 ラッチアップのテストサービスは、市場の多くのベンダーが行うことができます。このテストは、CMOS ICのSCRの構造をアクティブ化する一連の試行によって実行できますが、関連するピンは、過電流が流れるときにチェックされます。 実験ロットから最初のサンプルを入手し、それらをラッチアップのテストラボに送ることをお勧めします。このラボでは、達成可能な最大限の電源を適用し、電流供給の監視を通じてラッチアップが発生するたびに、チップの入力と出力に電流供給を提供します。 CMOSの利点は次のとおりです。 TTLに対するCMOSの主な利点は、優れたノイズマージンと消費電力の削減です。これは、VDDからGNDへの直線的な導通レーンがなく、入力条件に基づく立ち下がり時間がないためです。そうすれば、デジタル信号の送信は、CMOSチップを介して簡単かつ低コストになります。 CMOSは、BIOSの設定に保存されるコンピューターのマザーボード上のメモリ量を説明するために使用されます。これらの設定には、主に日付、時刻、およびハードウェアの設定が含まれます CMOSが両方の方法でアクティブに駆動する場合の出力 CMOSの欠点は次のとおりです。 補完的なMOSプロセスは広く実装されており、ほぼすべてのデジタルロジックアプリケーションのNMOSおよびバイポーラプロセスに根本的に取って代わっています。 CMOS技術は、次のデジタルIC設計に使用されています。 したがって、 CMOSトランジスタは非常に有名です 電力を効率よく使うからです。ある状態から別の状態に変化するときはいつでも、電力を使用しません。また、相補型半導体は相互に作用してo / p電圧を停止します。その結果、より少ない熱を提供する低電力設計が実現します。この理由により、これらのトランジスタは、カメラセンサー内のCCDなどの他の以前の設計を変更し、現在のほとんどのプロセッサで使用されています。コンピュータ内のCMOSのメモリは、BIOS設定と時刻と日付の情報を格納する一種の不揮発性RAMです。 あなたはこの概念をよりよく理解していると思います。さらに、この概念に関する質問や エレクトロニクスプロジェクト 、下のコメントセクションにコメントして、貴重な提案をしてください。ここにあなたへの質問があります、なぜCMOSがNMOSよりも好ましいのですか? 入力 論理入力 出力 論理出力 0 v 0 Vdd 1 Vdd 1 0 v 0 CMOSNANDゲート

に B プルダウンネットワーク プルアップネットワーク 出力Y 0 0 オフ オン 1 0 1 オフ オン 1 1 0 オフ オン 1 1 1 オン オフ 0 CMOSNORゲート

に B Y 0 0 1 0 1 0 1 0 0 1 1 0 CMOS製作

CMOSバッテリーの寿命

CMOSバッテリーの故障症状

CMOS特性

CCD対CMOS

一部のアプリケーションでは、CMOSセンサーは最近、CCDデバイスとほぼ同等になるまで改善されています。一般的に、CMOSカメラは高価ではなく、バッテリーの寿命が長いです。CMOSでのラッチアップ

利点

TTLは、バイポーラトランジスタがDCパルスで動作するデジタル論理回路です。通常、いくつかのトランジスタ論理ゲートは単一のICで構成されています。短所

CMOSアプリケーション