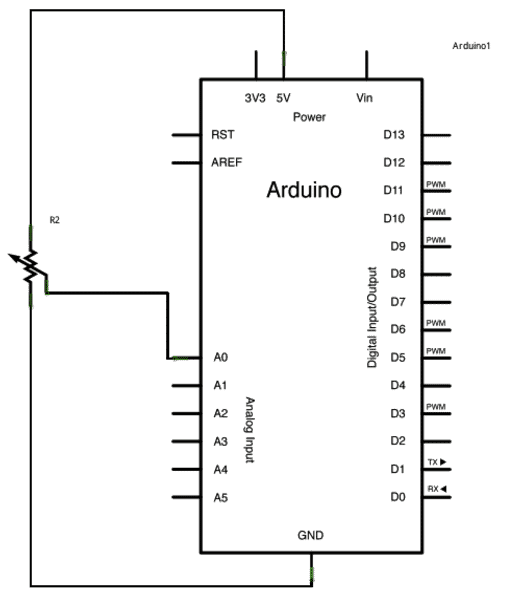

金属酸化物半導体トランジスタまたは MOS トランジスタは、ロジック チップ、プロセッサ、および最新のデジタル メモリの基本的なビルディング ブロックです。これは多数キャリア デバイスであり、ソースとドレインの間の導電チャネル内の電流は、ゲートへの印加電圧によって変調されます。この MOS トランジスタは、さまざまなアナログ & ミックスド シグナル IC で重要な役割を果たします。このトランジスタは非常に適応性が高く、アンプ、スイッチ、または 抵抗器 .いいえ トランジスタ PMOSとNMOSの2種類に分類されます。したがって、この記事では概要について説明します NMOSトランジスタ – 製造、回路および作業。

NMOSトランジスタとは?

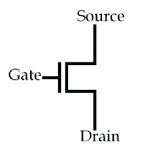

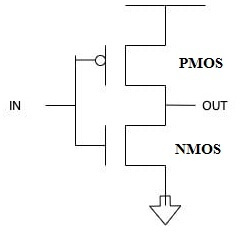

NMOS(nチャネル金属酸化物半導体)トランジスタは、ゲート領域にn型ドーパントが利用されるトランジスタの一種である。ゲート端子に正の (+ve) 電圧を加えると、デバイスがオンになります。このトランジスタは主に CMOS (相補型金属酸化膜半導体) 設計 & ロジック & メモリ チップにも。 PMOSトランジスタと比較して、このトランジスタは非常に高速であるため、より多くのトランジスタを1つのチップに配置できます。 NMOS トランジスタの記号を以下に示します。

NMOSトランジスタはどのように機能しますか?

NMOSトランジスタの働きは次のとおりです。 NMOSトランジスタが無視できない電圧を受け取ると、閉回路を形成します。これは、ソース端子からドレインへの接続がワイヤとして機能することを意味します。したがって、電流はゲート端子からソースに流れます。同様に、このトランジスタが約0Vの電圧を受けると、ソース端子からドレインへの接続が切断されることを意味する開回路を形成するため、電流はゲート端子からドレインに流れます。

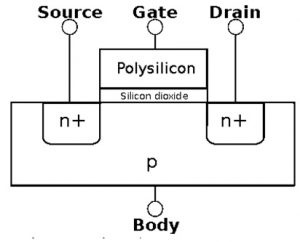

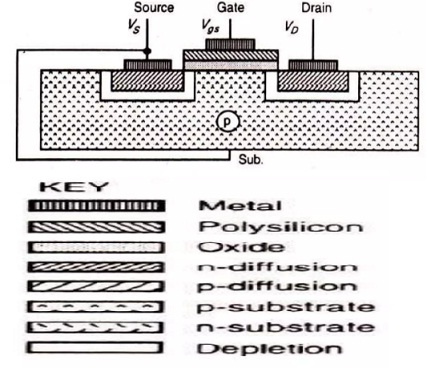

NMOSトランジスタの断面図

一般に、NMOSトランジスタは、ソースとドレインとして知られるゲートに隣接する2つのn型半導体領域によって、p型ボディで簡単に構築されます。このトランジスタには、ソース端子とドレイン端子間の電子の流れを制御する制御ゲートがあります。

このトランジスタでは、トランジスタのボディが接地されているため、ソースとドレインのPN接合がボディに向かって逆バイアスされています。ゲート端子の電圧が増加すると、電界が増加し始め、Si-SiO2 界面のベースに自由電子が引き寄せられます。

電圧が十分に高くなると、電子が巻き上げられてすべての正孔が埋められ、チャネルとして知られるゲートの下の薄い領域が反転して n 型半導体として機能します。これにより、電流の流れが可能になり、ソース端子からドレインまでの導電レーンが作成されるため、トランジスタがオンになります。ゲート端子が接地されている場合、逆バイアス接合部に電流が流れないため、トランジスタはオフになります。

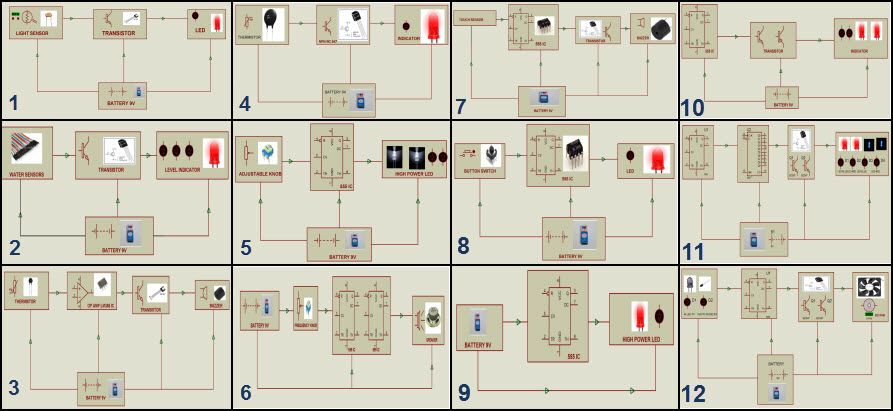

NMOSトランジスタ回路

PMOS および NMOS トランジスタを使用した NOT ゲートの設計を以下に示します。 NOT ゲートを設計するには、pMOS トランジスタをソースに接続し、nMOS トランジスタをグランドに接続して、pMOS と nMOS トランジスタを組み合わせる必要があります。したがって、回路は最初のCMOSトランジスタの例になります。

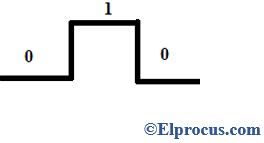

NOT ゲートは、反転入力を出力として生成する論理ゲートの一種です。このゲートはインバータとも呼ばれます。入力が「0」の場合、反転出力は「1」になります。

入力がゼロの場合、上部のpMOSトランジスタに行き、下部のnMOSトランジスタに下がります。入力値「0」がpMOSトランジスタに到達すると、「1」に反転します。したがって、ソースへの接続は停止します。したがって、ドレイン (GND) への接続も閉じている場合、論理値「1」が生成されます。 nMOS トランジスタは入力値を反転しないことがわかっているため、ゼロ値をそのまま取り、ドレインに開回路を作ります。そのため、論理値 1 がゲートに対して生成されます。

同様に、入力値が「1」の場合、この値は上記の回路の両方のトランジスタに送信されます。 「1」値が pMOS トランジスタを受け取ると、「o」に反転します。その結果、ソースへの接続が開かれます。 nMOS トランジスタが「1」の値を受け取ると、それは反転しません。そのため、入力値は 1 のままです。 1 つの値が nMOS トランジスタによって受信されると、GND への接続が閉じられます。したがって、出力として論理「0」を生成します。

製作工程

NMOS トランジスタの製造プロセスには多くのステップが含まれます。同じプロセスを PMOS トランジスタと CMOS トランジスタに使用できます。この製造で最も頻繁に使用される材料は、ポリシリコンまたは金属です。 NMOSトランジスタの段階的な製造工程を以下に説明する。

ステップ1:

ホウ素材料をドーピングするだけで、薄いシリコンウェーハ層が P 型材料に変わります。

ステップ2:

完全な p 型基板上に厚い SiO2 層を成長

ステップ3:

ここで、厚い Sio2 層の上にフォトレジストを介して表面をコーティングします。

ステップ4:

その後、この層は、拡散がトランジスタ チャネルと一緒に発生する領域を記述するマスクを使用して UV 光にさらされます。

ステップ5:

これらの領域は、下にある Sio2 と相互にエッチングされ、マスクを通して定義されたウィンドウ内にウェーハの表面が露出するようにします。

ステップ6:

残留フォトレジストが分離され、薄い SiO2 層が、通常、チップの全面に 0.1 マイクロメートル成長します。次に、この上にポリシリコンを配置してゲート構造を形成します。フォトレジストを完全なポリシリコン層の上に置き、マスク全体に紫外線を照射します2。

ステップ 7:

ウェーハを最高温度まで加熱することにより、拡散が達成され、リンなどの目的の n 型不純物を含むガスが通過します。

ステップ8:

厚さ 1 マイクロメートルの二酸化シリコンを全体に成長させ、その上にフォトレジスト材料を配置します。マスク 3 を介して紫外光 (UV) をゲートの優先領域に照射し、ソースおよびドレイン領域をエッチングしてコンタクト カットを作成します。

ステップ9:

次に、アルミニウムのような金属を幅 1 マイクロメートルの表面に配置します。もう一度、フォトレジスト材料を金属全体に成長させ、マスク 4 を介して UV 光にさらします。最終的な NMOS 構造を以下に示します。

PMOS対NMOSトランジスタ

PMOS トランジスタと NMOS トランジスタの違いについては、以下で説明します。

| PMOSトランジスタ | NMOSトランジスタ |

| PMOSトランジスタは、Pチャネル金属酸化膜半導体トランジスタの略です。 | NMOSトランジスタは、Nチャネル金属酸化膜半導体トランジスタの略です。 |

| PMOSトランジスタのソースとドレインは単純にn型半導体で作られています | NMOSトランジスタのソースとドレインは、単純にp型半導体で作られています。 |

| このトランジスタの基板はn型半導体で作られています | このトランジスタの基板はp型半導体で作られています |

| PMOS の電荷キャリアの大部分は正孔です。 | NMOS の電荷キャリアの大部分は電子です。 |

| NMOS と比較して、PMOS デバイスは小さくありません。 | NMOS デバイスは、PMOS デバイスに比べてかなり小さいです。 |

| PMOS デバイスは、NMOS デバイスに比べて高速に切り替えることはできません。 | PMOS デバイスと比較して、NMOS デバイスはより高速に切り替えることができます。 |

| PMOSトランジスタは、ゲートに低電圧が供給されると導通します。 | NMOSトランジスタは、ゲートに高電圧が供給されると導通します。 |

| これらは、ノイズに対してより耐性があります。 | PMOS と比較すると、これらはノイズの影響を受けません。 |

| このトランジスタのしきい値電圧 (Vth) は負の量です。 | このトランジスタのしきい値電圧 (Vth) は正の量です。 |

特徴

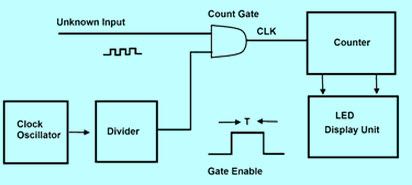

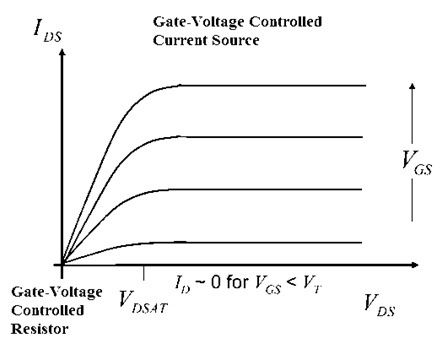

の NMOSトランジスタのI-V特性 以下に示します。ゲートとソース端子間の電圧 'V GS ' & また、ソースとドレインの間 'V DS 」。だから、私の間の曲線 DS とV DS ソースの端子を接地し、初期 VGS 値を設定し、V をスイープするだけで達成されます。 DS 「0」から V によって与えられる最大 DC 電圧値まで DD Vを踏むとき GS 「0」から V までの値 DD .したがって、Vが非常に低い場合 GS 、私 DS は非常に小さく、直線的な傾向があります。 Vのとき GS 価値が高くなり、私は DS 強化し、V に以下の依存関係があります GS & の DS ;

Vの場合 GS V 以下 TH の場合、トランジスタはオフ状態になり、開回路のように動作します。

Vの場合 GS Vより大きい TH の場合、2 つの動作モードがあります。

Vの場合 DS Vより小さい GS - の TH 、その後、トランジスタは線形モードで動作し、抵抗として機能します (R オン )。

IDS = u 効果 ハ 牛 W/L [(V GS - の TH )の DS – ½ V DS ^2]

どこ、

「µeff」は、電荷キャリアの実効移動度です。

「COX」は、単位面積あたりのゲート酸化膜の静電容量です。

W & L は、対応するチャネルの幅と長さです。 R オン 値は、次のようにゲートの電圧によって単純に制御されます。

R オン = 1/インチ n ハ 牛 W/L [(V GS - の TH )の DS – ½ V DS ^2]

VDSがV以上の場合 GS - の TH 、その後、トランジスタは飽和モード内で動作します

私 DS =あなた n ハ 牛 W/L [(V GS - の TH )^2 (1+λ V DS ]

この地域で私が DS が高い場合、電流は V に最小限依存します。 DS ただし、その最高値は VGS によって単純に制御されます。チャネル長変調「λ」は、ピンチオフによるトランジスタの VDS 内の増加による IDS 内の上昇を説明します。このピンチオフは、両方の V DS とV GS ドレイン領域に近い電界パターンを決定し、自然な供給電荷キャリアの方向を変更します。この効果は、効率的なチャネルの長さを削減し、I を増加させます。 DS .理想的には、「λ」は「0」に等しいので、 DS V から完全に独立している DS 飽和領域内の値。

したがって、これはすべてについてです NMOSの概要 トランジスタ – 加工と回路。 NMOS トランジスタは、論理ゲートやその他のさまざまなデジタル回路の実装において重要な役割を果たします。これは、主にロジック回路、メモリ チップ、および CMOS 設計の設計に使用される超小型電子回路です。 NMOS トランジスタの最も一般的なアプリケーションは、スイッチと電圧増幅器です。 PMOSトランジスタとは何ですか?