現在存在するFETの2つの主なタイプは次のとおりです。 JFETおよびMOSFET。

MOSFETはさらに空乏タイプと エンハンスメントタイプ。 これらのタイプはどちらもMOSFETの基本的な動作モードを定義しますが、MOSFETという用語自体は金属酸化物半導体電界効果トランジスタの略語です。

2つのタイプは動作特性が異なるため、それぞれを別々の記事で評価します。

エンハンスメントMOSFETとデプレッションMOSFETの違い

基本的に、エンハンスメントMOSFETとは異なり、空乏型MOSFETは、ゲート-ソース端子(VGS)の両端に0Vが存在する場合でもオン状態になります。

拡張MOSFETの場合、ゲート-ソース間電圧(VGS)は、ゲート-ソース間しきい値電圧(VGS(th))を上回っている必要があります。 それを実施させるために 。

ただし、Nチャネル空乏MOSFETの場合、そのVGS(th)値は0 Vを超えます。これは、VGS = 0 Vであっても、空乏MOSFETが電流を流すことができることを意味します。これをオフにするには、空乏MOSFETのVGSをVGS(th)(負)未満に下げる必要があります。

今回の記事では、JFETと同等の特性を持つと言われる空乏型MOSFETについて説明します。類似性は、I付近のカットオフと飽和の間ですDSS。

基本構造

図5.23にnチャネル空乏型MOSFETの基本的な内部構造を示します。

シリコンベースを使用して作成されたp型材料のブロックを見つけることができます。このブロックは基板と呼ばれます。

基板は、MOSFETが構築されるベースまたは基盤です。一部のMOSFETの場合、内部で「ソース」端子にリンクされています。また、多くのデバイスは、図5.23に示すように、4端子MOSFETを備えたSSの形で追加の出力を提供します。

同じ図に示すように、ドレイン端子とソース端子は、導電性接点を介してnドープされた場所に接続され、nチャネルを介して接続されます。

ゲートは金属層にも接続されていますが、二酸化シリコン(SiO)の微細な層を介してnチャネルから絶縁されています。二)。

SiO二誘電体と呼ばれる独自の絶縁特性を備えており、外部から印加された電界に応答して、誘電体自体の中に反対の電界を生成します。

絶縁層であるため、材料はSiO二次の重要な情報を提供します。

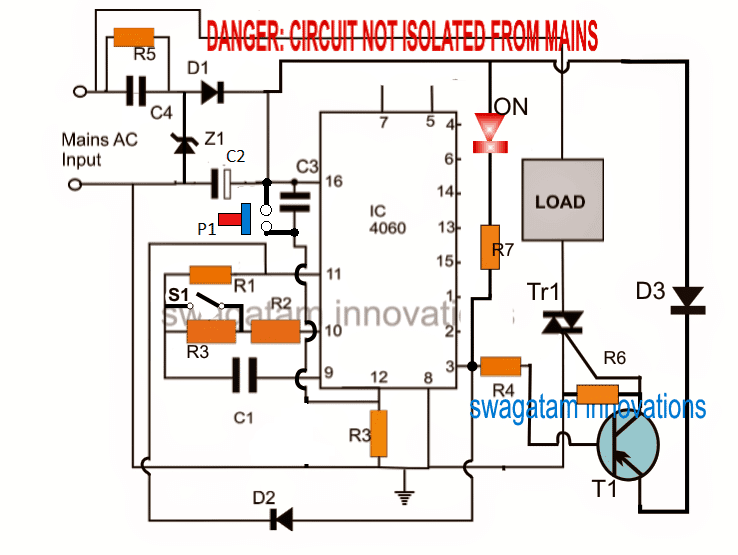

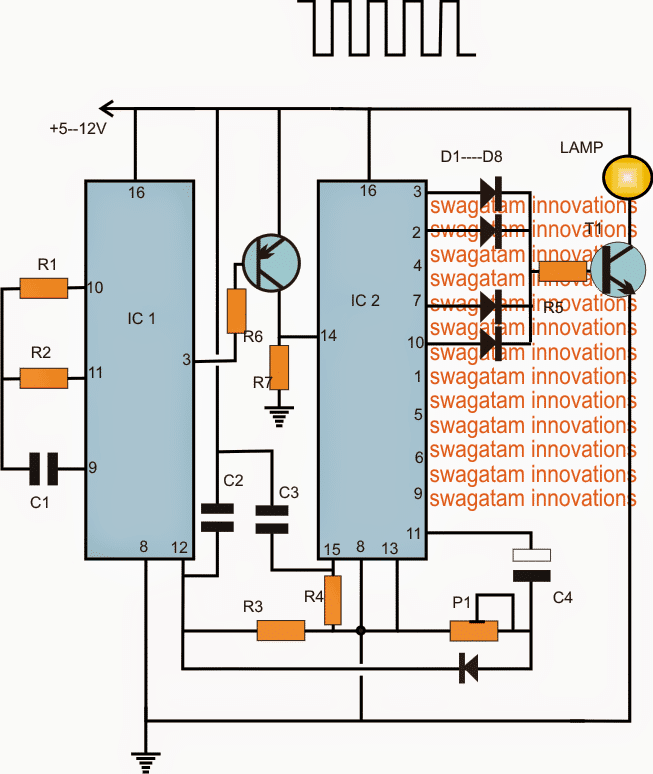

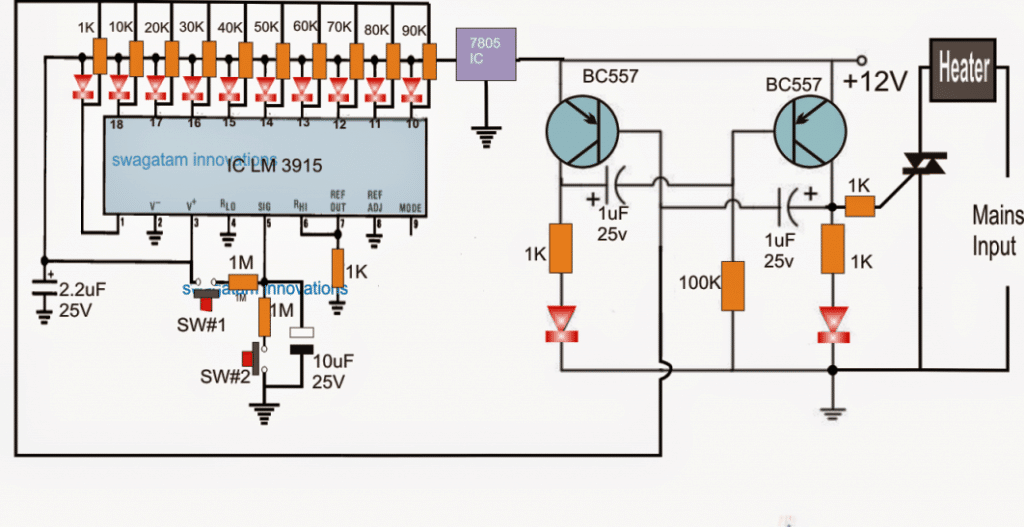

“ストロボライトの作り方 ”

この材料を使用すると、ゲート端子とMOSFETチャネルの間に完全な絶縁が確立されます。

また、SiOのせいです二、MOSFETのゲートは、非常に高度な入力インピーダンスを特徴とすることができます。

この重要な高入力インピーダンス特性により、ゲート電流IGDCバイアスMOSFET構成では、実質的にゼロアンペアです。

基本的な操作と特徴

図5.24に示すように、ゲートからソースへの電圧は、2つの端子を相互に接続することによってゼロボルトに構成されていますが、電圧VはDSドレイン端子とソース端子の間に適用されます。

上記の設定では、ドレイン側は、JFETチャネルを流れる等価電流とともに、nチャネルの自由電子によって正の電位を確立します。また、結果として生じる電流VGS= 0VはまだIとして識別されていますDSS、図5.25に示すように

図5.26では、ゲートソース電圧Vがわかります。GS-1Vの形で負の電位が与えられます。

この負の電位は、電子をpチャネル基板に向かって押し付け(電荷が反発するため)、pチャネル基板から正孔を引き出そうとします(反対の電荷が引き付けられるため)。

この負のバイアスVの大きさに応じてGSつまり、正孔と電子の再結合が起こり、伝導に利用できるnチャネル内の自由電子が減少します。負のバイアスのレベルが高いほど、組換え率が高くなります。

その結果、上記の負のバイアス条件が増加すると、ドレイン電流が減少します。これは、Vについて図5.25で証明されています。GSVのレベルGS= -1、-2など、-6Vのピンチオフマークまで。

結果としてのドレイン電流は、伝達曲線プロットとともに、 JFET。

さて、正のVについてGS値が正の場合、逆リーク電流のために、ゲート正はp型基板から過剰な電子(自由キャリア)を引き付けます。これにより、加速する粒子間で衝突が発生することにより、新しいキャリアが確立されます。

ゲート-ソース間電圧は正の速度で上昇する傾向があるため、上記と同じ理由で図5.25に示すように、ドレイン電流は急激に増加します。

Vの曲線間に生じたギャップGS= 0VおよびVGS= +1は、Vの1-V変動により電流が増加した量を明確に示しますGS

ドレイン電流が急速に上昇するため、最大定格電流に注意する必要があります。そうしないと、正のゲート電圧制限を超える可能性があります。

たとえば、図5.25に示されているデバイスタイプの場合、Vを適用します。GS= + 4Vにより、ドレイン電流が22.2 mAで上昇し、デバイスの最大ブレークダウン制限(電流)を超えている可能性があります。

上記の条件は、正のゲート-ソース間電圧を使用すると、Vの場合とは対照的に、チャネル内の自由キャリアの量に大きな影響を与えることを示しています。GS= 0V。

これが、ドレインまたは転送特性の正のゲート電圧領域が一般に次のように知られている理由です。 エンハンスメントリージョン 。この領域は、カットオフとIの飽和レベルの間にあります。DSSまたは空乏領域。

問題の例を解決する

利点とアプリケーション

ゲートからソースへの電圧がゼロに応答してドレイン電流がゼロに低下するエンハンスメントモードMOSFETとは対照的に、最新の空乏モードFETは、ゲート電圧がゼロの顕著な電流を特徴としています。正確には、ドレインからソースへの抵抗は通常、ゼロ電圧で100オームです。

上のグラフに示されているように、オン抵抗rds(オン)対アナログ信号範囲は、実質的にフラットな応答のように見えます。この特性は、これらの高度な空乏型デバイスの低容量レベルと相まって、オーディオおよびビデオスイッチングアプリケーションのアナログスイッチとして特に理想的です。

デプレッションモードMOSFETの「ノーマルオン」属性により、デバイスを単一のFET電流レギュレータに完全に適合させることができます。

そのような回路例の1つを次の図に示します。

Rs値は、次の式を使用して決定できます。

Rs= VGSオフ[1-(私D/私DSS)1/2] / 私D

どこ 私D は、出力に必要な安定化電流の量です。

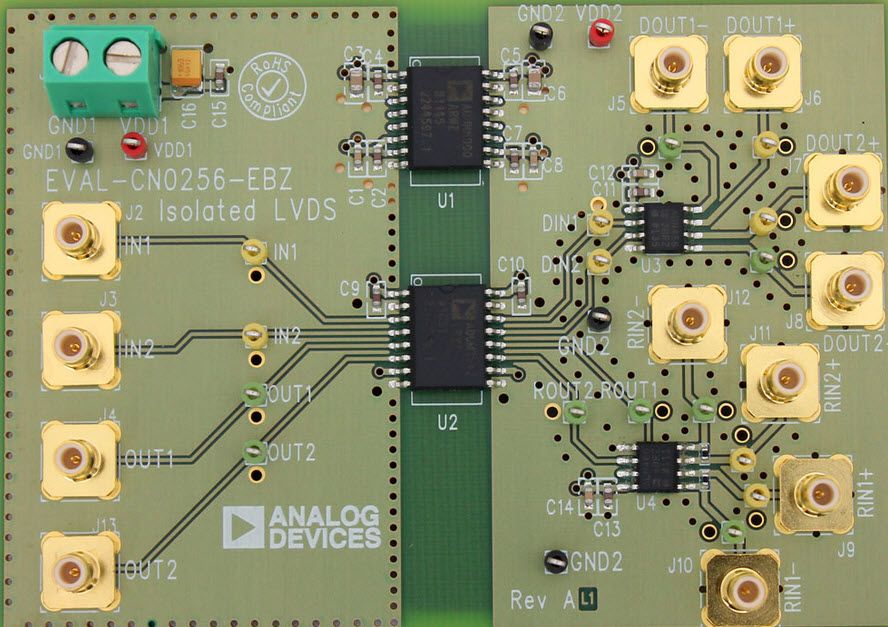

電流源アプリケーションにおける空乏モードMOSFETの主な利点は、ドレイン容量が最小であるため、低入力リーク、中速(> 50 V / us)回路のバイアスアプリケーションに適しています。

下の図は、ダブル低リーク機能FETを使用した低入力リーク電流差動フロントエンドを示しています。

一般的に言えば、JFETのいずれかの側はID = 500uAでバイアスされます。したがって、充電補償と浮遊容量のために得られる電流は、2ID、またはこのような場合は1.0mAに制限されます。 JFETの対応する機能は、製造実績があり、データシートで保証されています。

Csは、入力段の「テール」電流源の出力容量を表します。この容量は、入力段がこのネットワーク全体で重要な信号交換を経験し、Csの充電電流が大きくなる可能性があるため、非反転増幅器では重要です。通常の電流源が使用されている場合、このテール容量は、非反転回路での顕著なスルーレート劣化の原因となる可能性があります(Csの充電電流が最小になる傾向がある反転アプリケーションと比較して)。

スルーレートの低下は次のように表すことができます。

1/1 +(Cs / Sc)

CsがCc(補償コンデンサ)よりも低い限り、スルーレートの変動はほとんどありません。 DMOS FETを使用すると、Csは約2pFになる可能性があります。この戦略により、スルーレートが大幅に向上します。 1〜5 mAを超える電流不足が必要な場合、デバイスをエンハンスメントモードにバイアスして、+ 2.5Vの最大VGSで最大20mAを生成し、最小出力容量が引き続き重要な側面となります。

以下の次のアプリケーションは、適切なエンハンスメントモード電流源回路を示しています。

「通常オン」のアナログスイッチは、電源電圧の障害時に標準状態が必要になる要件のために構築できます。たとえば、テストツールの自動レンジングや、スイッチオン時の論理回路の正確な起動を保証するためです。

デバイスの負のしきい値電圧が低下すると、基本的なドライブの前提条件が提供され、最小限の電圧での作業が可能になります。

以下の回路は、空乏モードDMOSアナログスイッチの一般的なバイアス係数を示しています。

デバイスのスイッチをオフにするには、ゲートに負の電圧が必要になります。そうは言っても、正のゲート電圧を使用してFETをさらに強化すると、オン抵抗を最小限に抑えることができ、特にエンハンスメントモード領域とデプレッションモード領域でそれが可能になります。

この応答は、次のグラフで確認できます。

ユニットの高周波ゲインは、その低い静電容量値とともに、「性能指数」の向上をもたらします。これは、VHFおよびUHF増幅において非常に重要な要素であり、FETのゲイン帯域幅積(GBW)を指定します。これは、次のように表すことができます。

GBW = gfs / 2 円周率 (Cに+ Cアウト)

pチャネル空乏型MOSFET

pチャネル空乏型MOSFETの構造は、図5.23に示すnチャネルバージョンの完全な逆です。つまり、下の図5.28aに示すように、基板はn型になり、チャネルはp型になります。

同じ図に示すように、端子の識別は変更されませんが、電圧と電流の極性が逆になります。ドレイン特性は、Vを除いて、図5.25に示すとおりです。DSこの場合、負の値を取得する符号。

ドレイン電流IDこの場合も正の極性を示します。これは、すでに方向を逆にしているためです。 VGS図5.28cに示すように、は反対の極性を示しています。これは理解できます。

VだからGS反転すると、図5,28bに示すように伝達特性の鏡像が生成されます。

つまり、ドレイン電流は正のVで増加しますGSVのカットオフポイントからの領域GS=私までのVpDSS、その後、Vの負の値として上昇し続けますGS上昇します。

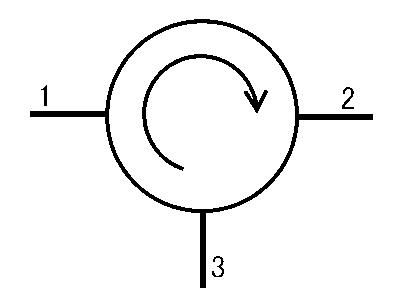

記号

nチャネルおよびpチャネルの空乏型MOSFETのグラフ表示は、上の図5.29で確認できます。

選択した記号がデバイスの実際の構造を表すことを目的としている方法を観察します。

ゲートとチャネルの間に(ゲート絶縁のために)直接相互接続がないことは、ゲートとシンボルの異なる端子の間のギャップによって象徴されます。

チャネルを表す垂直線は、ドレインとソースの間に接続され、基板によって「保持」されます。

上の図では、チャネルのタイプごとに2つのグループの記号が示されています。これは、一部のデバイスでは基板に外部からアクセスできる場合もあれば、見えない場合があることを強調するためです。

MOSFET(エンハンスメントタイプ)

空乏型とエンハンスメント型のMOSFETは、内部構造と機能モードが似ていますが、特性がかなり異なる場合があります。

主な違いは、カットオフ動作のゲート-ソース間電圧の特定のレベルに依存するドレイン電流です。

正確には、nチャネルエンハンスメントタイプのMOSFETは、通常は空乏タイプのMOSFETに影響を与える可能性のある負の電位範囲ではなく、正のゲート/ソース電圧で動作できます。

基本構造

以下でnチャネルエンハンスメント型MOSFETを視覚化できます

図5.31。

p型材料セクションは、シリコンベースを介して作成され、以前に学習したように、基板と呼ばれます。

この基板は、空乏型MOSFETのソースピンで内部に接続されている場合もありますが、電位レベルの外部制御を可能にするための4番目のリードとして終端されている場合もあります。

ソース端子とドレイン端子は、通常どおり、金属接点を使用してnドープ領域に結合されます。

ただし、図5.31では、2つのnドープ領域間のチャネルが欠落していることを視覚化することが重要な場合があります。

これは、空乏型とエンハンスメント型のMOSFETの内部レイアウト間の基本的な相違点、つまりデバイスの一部であると思われる固有のチャネルがないことと見なすことができます。

SiO2層はまだ普及していることがわかります。これにより、ゲート端子の金属ベースとドレインとソースの間の領域が確実に分離されます。ただし、ここでは、p型材料セクションから離れて立っているのを目撃することができます。

上記の説明から、エンハンスメントタイプのMOSFETのドレイン/ソース間のチャネルが欠落していることを除いて、空乏化およびエンハンスメントMOSFETの内部レイアウトにはいくつかの類似点があると結論付けることができます。

基本的な操作と特徴

エンハンスメントタイプのMOSFETの場合、VGSに0 Vが導入されると、nチャネル(多くのフリーキャリアを運ぶことが知られている)が欠落しているため、電流出力がゼロになります。これは、空乏タイプとはまったく異なります。 ID = IDSSのMOSFETの。

ドレイン/ソース端子間のパスが欠落しているためにこのような状況では、電子の形で大量のキャリアがドレイン/ソースに蓄積できません(nドープ領域のため)。

VDSに正の電位を印加し、VGSをゼロボルトに設定し、SS端子をソース端子と短絡すると、実際には、nドープ領域とp基板の間にいくつかの逆バイアスされたpn接合が見つかり、ソースにドレインします。

図5.32に、VDSとVGSに0 Vを超える正の電圧を印加して、ドレインとゲートをソースに対して正の電位にする条件を示します。

上図に示すように、ゲートの正の電位は、SiO2層のエッジに沿ってp基板の穴を押し、その位置を離れて、p基板の領域に深く入ります。これは、互いに反発する同様の電荷のために発生します。

これにより、正孔のないSiO2絶縁層の近くに空乏領域が作成されます。

それにもかかわらず、材料の少数キャリアであるp基板電子は正のゲートに向かって引っ張られ、SiO2層の表面に近い領域に集まり始めます。

SiO2層の絶縁特性により、負のキャリアは負のキャリアがゲート端子で吸収されるのを防ぎます。

VGSのレベルを上げると、SiO2表面に近い電子密度も増加し、最終的に誘導されたn型領域がドレイン/ソース全体で定量化可能な伝導を可能にするまで続きます。

ドレイン電流の最適な増加を引き起こすVGSの大きさは、しきい値電圧と呼ばれます。 記号VTで示されます 。データシートでは、これをVGS(Th)として見ることができます。

上で学習したように、VGS = 0にチャネルがなく、正のゲート-ソース間電圧印加で「拡張」されているため、このタイプのMOSFETは拡張タイプMOSFETとして知られています。

デプレッションタイプとエンハンスメントタイプの両方のMOSFETがエンハンスメントタイプの領域を示すことがわかりますが、この用語は 強化 後者には、拡張モードの操作を使用して特に機能するため、が使用されます。

これで、VGSがしきい値を超えると、フリーキャリアの濃度が誘導されたチャネルでブーストされます。これにより、ドレイン電流が増加します。

一方、VGSを一定に保ち、VDS(ドレイン-ソース間電圧)レベルを上げると、JFETや空乏型MOSFETでも通常発生するように、最終的にMOSFETが飽和点に到達します。

図5.33に示すように、ドレイン電流IDは、ピンチオフプロセスの助けを借りて横ばいになります。これは、誘導チャネルのドレイン端に向かって狭いチャネルで示されます。

図5.33のMOSFETの端子電圧にキルヒホッフの電圧法則を適用すると、次のようになります。

VGSが特定の値(たとえば8 V)に一定に保たれ、VDSが2Vから5Vに上昇した場合、式(1)による電圧VDGは次のようになります。 5.11は-6から-3Vに低下し、ゲート電位はドレイン電圧に対してますます正になります。

この応答は、自由キャリアまたは電子が誘導されたチャネルのこの領域に向かって引っ張られることを禁止し、その結果、チャネルの有効幅が低下します。

最終的に、チャネル幅はピンチオフのポイントまで減少し、以前の空乏MOSFETの記事ですでに学習したのと同様の飽和状態に達します。

つまり、固定VGSを使用してVDSをさらに増やしても、故障状況に達するまでIDの飽和レベルには影響しません。

図5.34を見ると、VGS = 8 Vの図5.33のようなMOSFETの場合、飽和は6 VのVDSレベルで発生することがわかります。正確には、VDS飽和レベルは適用されたVGSレベルに次のように関連付けられます。

したがって、間違いなく、VT値が固定されている場合、VGSのレベルを上げると、飽和レベルの軌跡を通じてVDSの飽和レベルが比例して高くなることを意味します。

上図の特性を参照すると、VTレベルは2 Vであり、ドレイン電流が0mAに低下していることがわかります。

したがって、通常、次のように言うことができます。

VGS値がエンハンスメント型MOSFETのしきい値レベルよりも小さい場合、そのドレイン電流は0mAです。

また、上の図から、VGSがVTから8 Vに上昇している限り、対応するIDの飽和レベルも0から10mAレベルに上昇していることがはっきりとわかります。

さらに、VGSの値が増加すると、VGSレベル間のスペースが増加し、ドレイン電流が無限に増加することがわかります。

ドレイン電流値は、次の非線形関係を通じて、VTよりも大きいVGSレベルのゲート-ソース間電圧に関連していることがわかります。

角括弧内に示されている用語は、IDとVGSの間の非線形の関係に関与する用語です。

項kは定数であり、MOSFETレイアウトの関数です。

この定数kの値は、次の式で求めることができます。

ここで、ID(on)とVGD(on)はそれぞれ、デバイスの特性に特に依存する値です。

下の次の図5.35では、ドレインと転送の特性が並べて配置されており、相互の転送プロセスが明確になっています。

基本的には、JFETおよび空乏型MOSFETについて前述したプロセスと同様です。

ただし、この場合、VGSVTのドレイン電流は0mAであることを覚えておく必要があります。

ここで、IDは顕著な量の電流を見る可能性があり、それは式(1)によって決定されるように増加します。 5.13。

ドレイン特性から伝達特性上の点を定義する際、飽和レベルのみを考慮することに注意してください。これにより、動作領域が、式(1)で確立された飽和レベルよりも高いVDS値に制限されます。 (5.12)。

pチャネルエンハンスメント型MOSFET

図5.37aに示すpチャネルエンハンスメント型MOSFETの構造は、図5.31に示す構造とは正反対です。

つまり、ドレインとソースの接合部の下に、n型基板とpドープ領域があることがわかります。

端子は引き続き確立されますが、電流の方向と電圧の極性はそれぞれ逆になります。

ドレイン特性は、図5.37cに示すようになり、VGSの大きさが連続的に負になることによって電流量が増加します。

伝達特性は、図5.35の伝達曲線の鏡面印象(ID軸の周り)であり、図5.37bに示すように、VTを超えるVGSの負の値が増えるにつれてIDが増加します。式(5.11)から(5.14)は、pチャネルデバイスにも同様に適切です。

参照:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

前:スパイ防止RF検出器回路–ワイヤレスバグ検出器 次へ:伝達特性