ザ・ 電界効果トランジスタ (FET)は、 電界 電流の流れを調整するために使用されます。これを実装するために、デバイスのゲート端子とソース端子の間に電位差が適用され、ドレイン端子とソース端子の間の導電率が変化して、これらの端子間に制御された電流が流れます。

FETは呼ばれます ユニポーラトランジスタ これらはシングルキャリアタイプのデバイスとして動作するように設計されているためです。さまざまなタイプの電界効果トランジスタが利用可能です。

シンボル

次の図では、nチャネルおよびpチャネルJFETのグラフィックシンボルを視覚化できます。

nチャネルデバイスの内側を指している矢印マークが、Iの方向を示していることがはっきりとわかります。G(ゲート電流)は、p-n接合が順方向にバイアスされたときに流れると想定されています。

pチャネルデバイスの場合、矢印記号の方向の違いを除いて、条件は同じです。

FETとBJTの違い

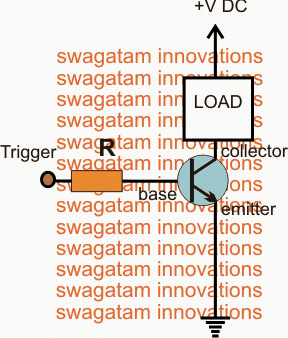

電界効果トランジスタ(FET)は、BJTトランジスタのアプリケーションを大幅に補完する幅広い回路アプリケーション向けに設計された3端子デバイスです。

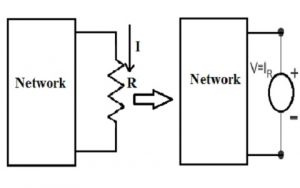

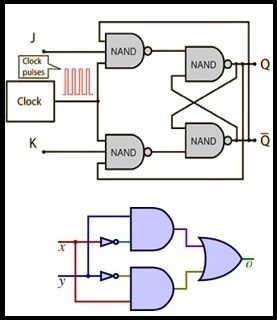

BJTとJFETの間には大きな違いがありますが、実際にはいくつかの一致する特性があり、以下の説明で説明します。これらのデバイスの主な違いは、BJTが図5.1aに示すように電流制御デバイスであるのに対し、JFETトランジスタは図5.1bに示すように電圧制御デバイスであるということです。

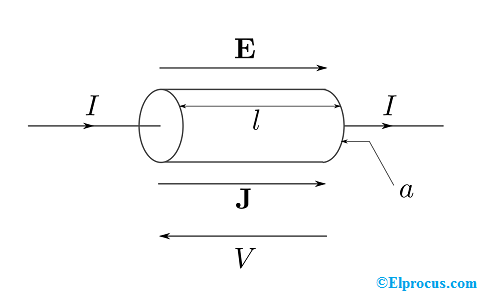

簡単に言えば、現在の私C図5.1aでは、Iのレベルの直接の関数です。B。 FETの場合、電流Iは電圧Vの関数です。GS図5.1bに示すように入力回路に与えられます。

どちらの場合も、出力回路の電流は入力回路のパラメータによって制御されます。一方の状況では電流レベル、もう一方の状況では印加電圧。

バイポーラトランジスタのnpnおよびpnpと同様に、nチャネルおよびpチャネルの電界効果トランジスタがあります。ただし、BJTトランジスタはバイポーラデバイスであり、接頭辞bi-は、伝導レベルが2つの電荷キャリア(電子と正孔)の関数であることを示していることを覚えておく必要があります。

一方、FETは ユニポーラデバイス これは、電子(nチャネル)または正孔(pチャネル)の伝導にのみ依存します。

「電界効果」というフレーズは、次のように説明できます。私たち全員が、物理的な接触なしに磁石に向かって金属のやすりを引き付ける永久磁石の力を知っています。同様に、FETの内部では、制御量と制御量の間に直接接触することなく、出力回路の伝導経路に影響を与える既存の電荷によって電界が生成されます。おそらく、FETの最も重要な機能の1つは、その高い入力インピーダンスです。

1から数百メガオームの範囲で、BJT構成の通常の入力抵抗範囲を大幅に上回ります。これは、リニアACアンプモデルを開発する際の非常に重要な属性です。

ただし、BJTは、入力信号の変動に対してより高い感度を備えています。つまり、出力電流の変化は、入力電圧の同じ量の変化に対して、通常、FETよりもBJTの方が大幅に大きくなります。

このため、BJTアンプの標準AC電圧ゲインは、FETと比較してはるかに高くなる可能性があります。

一般的に言えば、FETはBJTよりもかなり熱弾性が高く、BJTに比べて構造が小さいことが多いため、集積回路としての埋め込みに特に適しています(IC)チップ。

一方、一部のFETの構造特性により、BJTよりも物理的接触に非常に敏感になる可能性があります。

より多くのBJT / JFET関係

- BJTVの場合BE= 0.7 Vは、その構成の分析を開始するための重要な要素です。

- 同様に、パラメータIG= 0 Aは通常、JFET回路の分析で最初に考慮されるものです。

- BJT構成の場合、IB多くの場合、決定する必要がある最初の要因です。

- 同様に、JFETの場合、通常はVです。GS。

この記事では、JFETまたは接合型電界効果トランジスタに焦点を当て、次の記事では、金属酸化物半導体電界効果トランジスタまたはMOS-FETについて説明します。

JFETの構造と特性

私たちが最初に学んだように、JFETには3つのリードがあります。それらの1つは、他の2つの間の電流の流れを制御します。

BJTと同様に、JFETでも、nデバイスはpデバイスに比べて効率的でユーザーフレンドリーである傾向があるため、nチャネルデバイスはpチャネルの対応物よりも目立つように使用されます。

次の図では、nチャネルJFETの基本構造または構造を示しています。 n型組成がp型層を横切る主要チャネルを形成していることがわかります。

n型チャネルの上部は、ドレイン(D)という名前の端子とオーミック接触を介して結合され、同じチャネルの下部も、ソース(S)という名前の別の端子とのオーミック接触を介して接続されます。

いくつかのp型材料は、ゲート(G)と呼ばれる端子と一緒にリンクされています。基本的に、ドレイン端子とソース端子がn型チャネルの両端に結合されていることがわかります。ゲート端子は、1対のpチャネル材料に結合されています。

jfetの両端に電圧が印加されていない場合、その2つのp-n接合にはバイアス条件がありません。この状況では、上の図に示すように、各接合部に空乏領域が存在します。これは、バイアスのないダイオードのp-n領域のように見えます。

水のアナロジー

JFETの動作と制御動作は、次の水の例えから理解できます。

ここで、水圧は、ドレインからソースに向かって印加される電圧の大きさと比較できます。

水の流れは電子の流れと比較することができます。蛇口の口はJFETのソース端子を模倣し、水が押し込まれる蛇口の上部はJFETのドレインを表しています。

タップノブはJFETのゲートのように機能します。タップノブが口の開口部の水の流れを制御するのと同じように、入力電位の助けを借りて、ドレインからソースへの電子(電荷)の流れを制御します。

JFET構造から、ドレイン端子とソース端子がnチャネルの両端にあることがわかります。この用語は電子の流れに基づいているため、次のように記述できます。

VGS= 0 V、VDSいくつかの正の値

図5.4では、正の電圧Vを見ることができます。DSnチャネル全体に適用されます。ゲート端子はソースに直接結合され、条件Vを作成します。GS= 0V。これにより、ゲート端子とソース端子を同じ電位にすることができ、バイアスのない状態で上の最初の図に示されているように、各p材料の下端の空乏領域が生じます。

電圧VとすぐにDD(= VDS)が適用されると、図5.4に示すように、電子がドレイン端子に向かって引っ張られ、従来の電流IDの流れが生成されます。

電荷の流れの方向は、ドレイン電流とソース電流の大きさが等しいことを示しています(ID=私S)。図5.4に示されている条件によると、電荷の流れはまったく制限されていないように見え、ドレインとソースの間のnチャネルの抵抗によってのみ影響を受けます。

両方のp型材料の上部付近で空乏領域が大きくなっていることがわかります。この領域のサイズの違いは、図5.5で説明できます。 nチャネルに均一な抵抗があると想像してみましょう。これは図5.5に示すセクションに分割できます。

現在の私D同じ図で指摘されているように、チャネルを介して電圧範囲を構築する場合があります。その結果、p型材料の上部領域は約1.5 Vのレベルで逆バイアスされ、下部領域は0.5Vだけ逆バイアスされます。

p-n接合がチャネル全体に沿って逆バイアスされる点は、同じ図に示されているように、ゼロアンペアのゲート電流を発生させます。私につながるこの特性G= 0AはJFETの重要な特性です。

VとしてDS電位は0から数ボルトに増加し、電流はオームの法則とIのプロットに従って増加しますD5行目DS図5.6で証明されているように見えることができます。

プロットの真直度の比較は、Vの値の小さい領域についてDS、抵抗は基本的に均一です。 VとしてDS図5.6でVPと呼ばれるレベルに上昇して近づくと、図5.4に示すように空乏領域が広がります。

これにより、チャネル幅が明らかに低下します。伝導経路が減少すると抵抗が増加し、図5.6の曲線が生じます。

曲線が水平になるほど抵抗が高くなり、抵抗が水平領域で「無限」オームに近づいていることを示します。 VのときDS図5.7に示すように、2つの空乏領域が「接触」するように見える程度まで増加すると、ピンチオフと呼ばれる状況が発生します。

Vの量DSこの状況を開発すると呼ばれます ピンチオフ 電圧とそれはVで表されますP図5.6に示すように。一般に、ピンチオフという言葉は、現在のIを意味するため、誤解を招く恐れがあります。Dは「ピンチオフ」され、0 Aに低下します。図5.6で証明されているように、この場合、これはほとんど明らかではありません。私DIとして特徴付けられる飽和レベルを保持しますDSS図5.6。

真実は、非常に小さなチャネルが存在し続けており、電流が非常に集中していることです。

IDが落ちないポイント ピンチオフ 図5.6に示すように飽和レベルを維持し、次の証明で確認されます。

ドレイン電流がないため、p-n接合に沿った逆バイアスの変化量を決定するためのnチャネル材料を介した多様な電位レベルの可能性が排除されます。最終的な結果は、トリガーされた空乏領域分布の喪失です。 ピンチオフ で開始する。

Vを上げるとDSV以上P、2つの空乏領域が互いに遭遇する密接な接触領域は、チャネルに沿って長さが増加します。ただし、IDレベルは基本的に変更されません。

したがって、瞬間VDSVよりも高いp、JFETは電流源の特性を取得します。

図5.8で証明されているように、JFETの電流はIで決定されますD=私DSS、しかし電圧VDSVPより高い値は、接続された負荷によって確立されます。

IDSS表記の選択は、ゲートからソースへのリンクが短絡しているのはドレインからソースへの電流であるという事実に基づいています。

さらに調査すると、次の評価が得られます。

私DSSはJFETの最大ドレイン電流であり、条件Vによって確立されます。GS= 0VおよびVDS> | VP |。

図5.6Vで注意してくださいGS曲線が完全に伸びる場合は0Vです。次のセクションでは、Vのレベルとして図5.6の属性がどのように影響を受けるかを学習します。GSさまざまです。

VGS <0V

ゲートとソースに印加される電圧はVGSとして示され、VGSはJFETの動作を制御します。

BJTを例にとると、Iの曲線と同じです。Cvs VこのIのさまざまなレベルで決定されますB、同様にIの曲線Dvs VDSさまざまなレベルのVGSJFETの対応物用に作成できます。

このため、ゲート端子は、ソース電位のレベルよりも低い電位に設定されます。

下の図5.9を参照すると、ゲート/ソース端子間に-1Vが印加され、Vが減少します。DSレベル。

負の電位バイアスVの目的GSVの状況に似た空乏領域を開発することですGS= 0、ただしVが大幅に低下した場合DS。

これにより、ゲートはより低いレベルのVで飽和点に到達します。DS図5.10に示すように(VGS= -1V)。

Iに対応する飽和度D減少していることがわかり、実際にはVとして減少し続けますGSよりネガティブになります。

図5.10から、ピンチオフ電圧がVとして放物線状に低下し続ける様子がはっきりとわかります。GSますますネガティブになります。

最後に、VGS= -Vp、それは最終的に0mAである飽和レベルを確立するのに十分に負になります。このレベルでは、JFETは完全に「オフ」になっています。

VのレベルGS私を引き起こすD0mAに到達することはVによって特徴付けられますGS= VP、ここで、VPは、nチャネルデバイスの場合は負の電圧、pチャネルJFETの場合は正の電圧です。

一般的に、ほとんどのJFETデータシートが表示されていることがあります ピンチオフ Vとして指定された電圧GS(オフ)Vの代わりにP。

上図のピンチオフ軌跡の右側の領域は、歪みのない信号を実現するために線形増幅器で従来使用されていた場所です。この地域は一般的に呼ばれます 定電流、飽和、または線形増幅領域。

電圧制御抵抗器

同じ図のピンチオフ軌跡の左側にある領域は、 オーミック領域または電圧制御抵抗領域。

この領域では、デバイスは実際には可変抵抗器として動作でき(たとえば、自動利得制御アプリケーションで)、その抵抗は印加されたゲート/ソース電位によって制御されます。

各曲線の傾きは、Vに対するJFETのドレイン/ソース抵抗も示していることがわかります。DS

負の電位でVGSを高くすると、各曲線の傾きはますます水平になり、それに比例して抵抗レベルが増加します。

次の式により、VGS電圧に対する抵抗のレベルの適切な初期近似を得ることができます。

pチャネルJFETの動作

以下に示すように、pチャネルJFETの内部レイアウトと構造は、pタイプとnタイプの材料領域が逆になっていることを除いて、nチャネルの対応物とまったく同じです。

電流の方向は、電圧VGSおよびVDSの実際の極性とともに、逆になっているように見えることもあります。 pチャネルJFETの場合、ゲート/ソース全体の正電位の増加に応じてチャネルが制約されます。

Vの二重添え字付きの表記DSVの負電圧が発生しますDS、図5.12の特性に示すように。ここで、あなたは私を見つけることができますDSS6 mAで、Vでピンチオフ電圧GS= + 6V。

Vのマイナス記号があるので戸惑わないでくださいDS。これは単に、ソースがドレインよりも高い電位を持っていることを示しています。

高Vの曲線がわかりますDSレベルは、制限されていないように見える値に突然上昇します。垂直方向に示されている上昇は、故障状況を表しています。これは、チャネルデバイスを流れる電流がこの時点で外部回路によって完全に制御されていることを意味します。

これは、nチャネルデバイスの図5.10では明らかではありませんが、十分に高い電圧の下での可能性があります。

この領域は、VがDS(最大)デバイスのデータシートに記載されており、デバイスは実際のVDS値は、任意のVについてこの記載された値よりも低いGS。

前:調査した5つのベスト40ワットアンプ回路 次へ:2N3055データシート、ピン配置、アプリケーション回路