MicroBlaze プロセッサは 2002 年に開発され、いくつかの複雑な機能を統合して、新しい市場の需要だけでなく、成長する市場の需要にも対応しています。そのため、MicroBlaze プロセッサはザイリンクスのローエンド ポートフォリオに不可欠な要素であり、Artix®-7 を含むより迅速なシステム開発を可能にします。 FPGA 、Spartan®-6、Zynq®-7000 AP SoC。このプロセッサは非常に柔軟に構成できるため、FPGA 内のエンベデッド プロセッサまたはマイクロコントローラとして使用したり、ARM Cortex-A9 ベースの Zynq-7000 AP SoC でコプロセッサとして使用したりできます。この記事では、以下に関する簡単な情報を提供します。 MicroBlaze プロセッサ – アーキテクチャとアプリケーションの操作。

Microblaze プロセッサとは何ですか?

主にザイリンクスの FPGA 向けに設計されたソフト マイクロプロセッサは、MicroBlaze プロセッサとして知られています。このプロセッサは、ザイリンクスの FPGA の汎用メモリおよびロジック ファブリック内に簡単に実装されます。このプロセッサは、RISC に基づく DLX アーキテクチャに似ており、さまざまな組み込みアプリケーションをサポートするように柔軟な相互接続システムを備えています。 MicroBlaze のメイン I/O バスと AXI インターコネクトは、マスター/スレーブ機能を備えたメモリ マップド トランザクション バスです。

MicroBlaze は、専用 LMB バスを使用してローカル メモリにアクセスし、オンチップ ストレージを迅速に提供します。このプロセッサの多くの部分は、キャッシュのサイズ、パイプライン メモリ管理ユニットの深さ、組み込み周辺機器およびバス インターフェイスなど、ユーザーが設定できます。

マイクロブレイズの特徴

の マイクロブレイズの特徴 e には以下が含まれます。 32 個の汎用レジスタがあります。

- 2 つのアドレッシング モードと 3 つのオペランドを含む 32 ビットの命令語があります。

- アドレスバスは 32 ビットです。

- 3 段階のパイプラインまたは 5 段階のパイプラインがあります。

- シフター付きALUブロックユニット。

- ハーバード アーキテクチャには、32 ビット データおよびアドレス バスが含まれます。

- データ インターフェイス & LMB またはローカル メモリ バス命令。

- AX14 および AX14 ストリーム インターフェイス。

- 浮動小数点ユニットとメモリ管理ユニット。

- ロックステップ対応です。

- デバッグ & トレース インターフェイス。

マイクロベイズ アーキテクチャ

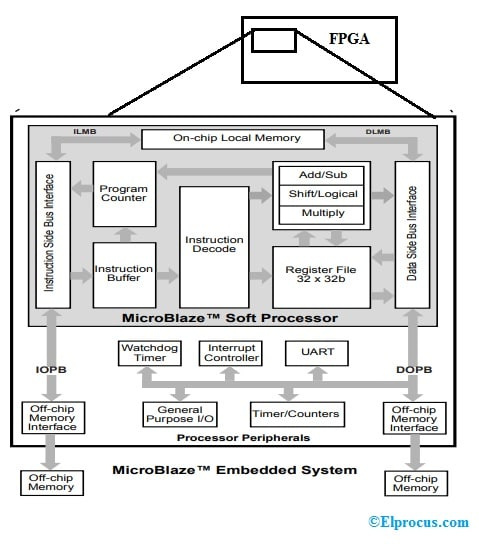

MicroBlaze プロセッサのブロック図を以下に示します。この MicroBlaze プロセッサは非常にカスタマイズ可能で、70 以上のデザイン オプションをサポートしています。このアーキテクチャは、永続的なハードウェア機能と、命令またはデータ キャッシュ、メモリ管理ユニット、浮動小数点ユニットなどの構成可能なオプションを示しています。

アン 組み込みシステム MicroBlaze プロセッサを中心に組み立てられたものには、主に MicroBlaze ソフト プロセッサ コア、オンチップ ローカル メモリ、標準バス インターコネクト、および OPB ペリフェラル (オンチップ ペリフェラル バス) が含まれます。 MicroBlaze プロセッサ システムは、主にローカル メモリによるプロセッサのコアから、いくつかの MicroBlaze を含む大規模なシステムにまで及びます。 プロセッサ 、外部メモリ、および多くの OPB ペリフェラル。

ソフト プロセッサ コア

MicroBlaze のソフト プロセッサ コアは、MicroBlaze エンベデッド システムの中心です。これは、次の機能を持つ非常に高速で効率的な 32 ビット RISC プロセッサです。

- 命令セットは直交です。

- データバスと命令バスを分離します。

- 32 ビットの汎用レジスタ。

- オプションの完全な 32 ビット バレル シフターがあります。

- 高速 OCM またはオンチップ メモリ & IBM の業界標準 OPB (オンチップ ペリフェラル バス) への組み込みインターフェイス。

Virtex-II 以降のデバイス内のインプリメンテーションでは、複数のハードウェアがサポートされます。

オンチップローカルメモリ

同期メモリは、オンチップ ブロック RAM を許可するために主に使用されるローカル メモリです。

標準バス相互接続

命令・データ側のバスインタフェースには、LMB(Local Memory Bus)と呼ばれるローカルメモリへのインタフェースとIBMのOn-chip Peripheral Busへのインタフェースがあります。そのため、ハーバード アーキテクチャに厳密に準拠したシステムを設計できます。それ以外の場合は、リソースを共有するために、バス アービターを介して組み合わせ内で単一の OPB を利用できます。

ローカル メモリ バスは、オンチップ ブロック RAM のシングル サイクル エントリを保証します。これは非常に効率的でシンプルなシングルマスター バス プロトコルであり、高速なローカル メモリとのインターフェイスに最適です。 OPB またはオンチップ ペリフェラル バスは、ペリフェラルと外部メモリを MicroBlaze プロセッサのコアに結合するのに最適な 32 ビットの幅広いマルチマスター バスです。

オンチップ ペリフェラル バス ペリフェラル

MicroBlaze ハードウェア システムは OPB ペリフェラルによって完成され、ウォッチドッグ タイマーまたはタイムベース、汎用タイマーまたはカウンター、I2C (割り込みコントローラー)、SRAM、フラッシュ メモリ、ZBT メモリ、BRAM、DDR、SDRAM、UART Lite などのさまざまなコントローラーなどのさまざまな機能を提供します。 、SPI、I2C、汎用 I/O、UART 16450/550、イーサネット 10/100 MAC。さらに、主にカスタム機能用のペリフェラルを追加および定義することもできます。それ以外の場合は、FPGA に存在するデザインへのインターフェイスです。

Microblaze 命令セット

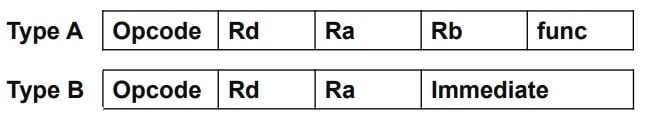

Microblaze 命令セットは、算術、論理、分岐、ロード/ストアなどです。すべての命令のサイズは固定されています。オペランドとして最大 3 つのレジスタを指定できます。 Microblaze には、次に示すタイプ A とタイプ B の 2 つの命令フォーマットがあります。

タイプ A 命令フォーマットは、主にレジスタ間命令に使用されます。したがって、オペコード、単一の宛先、および 2 つのソース レジスタが含まれます。タイプ B 命令フォーマットは、主に、オペコード、シングル デスティネーション、およびシングル ソース レジスタと 16 ビットの即値ソースを含むレジスタ即値命令に使用されます。

上記の 2 つの命令形式では、オペコードはオペレーション コード、Rd は 5 ビットでエンコードされたデスティネーション レジスタ、Ra と Rb はそれぞれ 5 ビットでエンコードされたソース レジスタ、Immediate は 16 ビットの値です。

算術命令

タイプ A およびタイプ B の算術命令を以下に示します。

タイプA

|

Rd、Ra、Rb を追加 追加 |

Rd = Ra+Rb、キャリー フラグの影響 |

|

ADD K Rd、Ra、Rb 追加して持ち歩く |

Rd = Ra+Rb、キャリー フラグは影響を受けません |

| RSUB Rd、Ra、Rb 逆減算 |

Rd = R-Rb、キャリー フラグは影響を受けません |

タイプB

|

ADD I Rd、Ra、Imm すぐに追加 |

Rd = Ra+signExtend32 (Imm) |

|

ADD IK Rd、Ra、Imm すぐに追加してキャリーを保持 |

Rd = Ra+ signExtend32 (Imm) |

| RSUBIK Rd、Ra、Imm 即値で逆減算 |

Rd = Ra+ signExtend32 (Imm) -Ra |

| SRA Rd、Ra 算術右シフト |

Rd = (Ra>>1) |

ロジック命令

タイプ A およびタイプ B の論理命令を以下に示します。

タイプA

|

またはRd、Ra、Rb 論理的または |

Rd = Ra| Rb |

|

AND Rd、Ra、Rb 論理和 |

Rd = Ra & Rb |

| XOR Rd、Ra、Rb 論理的xor |

Rd = Rb ^ Rb |

| ANDN Rd、Ra、Rb 論理的ではない |

Rd = Ra & (Rb) |

タイプB

|

ORI Rd、Ra、Imm 即時との論理和 |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd、Ra、Imm 即時との論理積 |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd、Ra、Imm 即時の論理 XOR |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm 即時の論理 AND NOT |

Rd = Ra & (signExtend32 (Imm)) |

分岐命令 - 無条件

プログラム カウンター レジスタを変更します。

| BRID Imm 即時遅延で即時分岐 |

PC = PC+ signExtend32 (Imm) 遅延スロットの実行を許可する |

| BRLID Rd, Imm 即時遅延による即時分岐およびリンク (関数呼び出し) |

Rd = PC PC = PC+& signExtend32 (Imm) 遅延スロットの実行を許可する |

| RTSD ラー、イム サブルーチンから戻る |

PC = Ra + signExtend32 (Imm) 遅延スロットの実行を許可する |

| RTID ラー、イム 割り込みからの復帰 |

PC = Ra + signExtend32 (Imm) 遅延スロットの実行を許可する MSR で割り込みイネーブルを設定する |

分岐命令 - 無条件 1

条件が満たされたときにプログラム カウンター レジスタを変更する

| BEQI ラー、イム 等しければ分岐 |

PC = PC+ signExtend32 (Imm) Ra = = 0 の場合 |

| MASH ラ、イム 等しくなければ分岐 |

Rd = PC PC = PC+& signExtend32 (Imm) らら! = 0 |

分岐命令 - 無条件 2

条件が満たされたときにプログラム カウンター レジスタを変更する

| BLTI ラ、イム より低い場合は分岐 |

PC = PC+ signExtend32 (Imm) Ra < 0 の場合 |

| BLEI ラー、イム より小さい場合に分岐 |

Rd = PC PC = PC+& signExtend32 (Imm) Ra!< = 0 の場合 |

| BGTI ラー、イム より大きい場合は分岐 |

PC = PC+ signExtend32 (Imm) Ra!> 0 の場合 |

| BGEI ラー、イム 等しい場合に分岐 |

PC = PC+signExtend32 (Imm) Ra!>= 0 の場合 |

ロード/ストア命令 - タイプ A

| LW Rd、Ra、Rb 単語を読み込む |

アドレス = Ra+Rb Rd = *住所 |

| SW Rd、Ra、Rb 単語を保存する |

アドレス – Ra+Rb *住所 = Rd |

タイプB

| LWI Rd、Ra、Imn 単語をすぐにロード |

アドレス = Ra + signExtend32 (Imm) Rd = *住所 |

| SW Rd、Ra、Imm 単語をすぐに保存 |

アドレス = Ra + signExtend32 (Imm) *住所 = Rd |

その他の指示

| IMM、IMM すぐに |

先行するタイプ B 命令の Imm を 32 ビットに拡張します。 |

| MFS Rd, Sa 特別目的レジスターからの移動 |

Rd = Sa Sa- 特殊目的レジスター、ソースオペランド

|

| MTS Sd、Ra 特別目的レジスターへの移動 |

Sd = Ra Sd – 特殊目的レジスター、宛先オペランド |

レジスター

MicroBlaze プロセッサのアーキテクチャは完全に直交しており、32 ビットの汎用レジスタと、プログラム カウンタやマシン ステータス レジスタなどの 32 ビットの専用レジスタが含まれています。

パイプライン アーキテクチャ

MicroBlaze は、フェッチ、デコード、および完了ステージを含む 3 ステージのパイプライン アーキテクチャを利用します。自動的に、データ転送、分岐、およびパイプライン ストールがハードウェア内で決定されます。

ロードまたはストア アーキテクチャ

MicroBlaze は、8 ビット (バイト)、16 ビット (ハーフワード)、および 32 ビット (ワード) の 3 つのデータ サイズのメモリをサポートします。そのため、メモリ アクセスは常にデータ サイズが整列されます。これは、ビッグ エンディアン アドレスのアドレスと、メモリにアクセスした後のラベル付け規則を使用するビッグ エンディアン プロセッサです。

割り込み

割り込みが発生すると、このプロセッサは現在の実行を終了し、割り込みベクトルアドレスへの分岐を通じて割り込み要求を管理し、実行する必要がある命令アドレスを格納します。このプロセッサは、MSR (マシン ステータス レジスタ) 内の IE (割り込み有効化) フラグをクリアすることにより、将来の割り込みを停止します。

マイクロブレイズはどのように機能しますか?

MicroBlaze プロセッサは 32 ビット バス幅をサポートし、このプロセッサ コアは RISC ベースのエンジンであり、メモリおよびデータ アクセス用の個別の命令を介して 32 ビット LUT RAM に基づくレジスタ ファイルを含みます。

このプロセッサは、オンチップ BlockRAM と外部メモリの両方を単純にサポートします。 IBM PowerPC に似ています。すべてのペリフェラルは同様の CoreConnect OPB バスを利用します。プロセッサのペリフェラルは、Virtex-II Pro の PowerPC とよく一致しています。

MicroBlaze プロセッサは、メモリ、ペリフェラル、およびインターフェイス機能の組み合わせを選択できる完全な柔軟性を提供し、単一の FPGA で必要な正確なシステムを低コストで提供します。

違い B/W Microblaze 対 Risc-V

の MicroBlaze と RISC v の違い 以下のものが含まれます。

|

マイクロブレイズ |

リスクV |

| これは、主にザイリンクス FPGA 用に設計されたソフト マイクロプロセッサ コアです。

|

RISC-V は、RISC の原則に基づいた命令セット アーキテクチャです。

|

| ハーバード RISC アーキテクチャを使用しています。 | 命令セット アーキテクチャを使用します。 |

| そのライセンスは独自のものです (Xilinx) | そのライセンスはオープンソースです。 |

| パイプラインの深さは 3 または 5 です。 | パイプラインの深さは 5 です。 |

| その性能は 280 DMIP です。 | その性能は 250 DMIP です。 |

| その速度は 235 MHz です。 | その速度は 250 MHz です。 |

| 1027 個の LUT があります。 | 4125 個の LUT があります。 |

| 使用されるテクノロジの実装は、Xilinx FPGA です。 | 使用されるテクノロジーの実装は FPGA/ASIC です。 |

マイクロブレイズの利点

の MicroBlaze の利点 以下のものが含まれます。

- 経済的です。

- 高度な構成が可能です。

- ARMに比べて性能が高い。

- 組み込み開発キットでサポートされています。

- ソフトです マイクロプロセッサ 芯。

- アプリケーションの迅速な配置を支援するために、このプロセッサには、マイクロコントローラ、リアルタイム、およびアプリケーション プロセッサのよく知られたプロセッサ クラスに関連する 3 つの固定構成が含まれています。

マイクロブレイズ アプリケーション

の MicroBlaze のアプリケーション 以下のものが含まれます。

- このプロセッサは、産業用、自動車用、医療用および民生用など、さまざまなアプリケーション要件を満たしています。

- MicroBlaze のアプリケーションは、ソフトウェアに基づく単純なステート マシンから、組み込みアプリケーションやインターネット ベースのアプライアンスで使用される複雑なコントローラーまで多岐にわたります。

- 産業用制御、オフィス オートメーション、自動車などの組み込みアプリケーション向けに最適化されています。

- MicroBlaze は、大規模なペリフェラル セットと通信して、中規模のアプリケーションに適合させることができます。

- このプロセッサのソフトな性質により、さまざまなアプリケーション向けにカスタマイズ可能であり、設計者はサイズに合わせて機能を交換して、医療、自動車、産業およびセキュリティ アプリケーションの価格と性能の目標を満たすことができます。

したがって、これはすべてについてです Microblaze の概要 プロセッサー。これは、フル機能の 32 ビット プログラマブル RISC ソフト プロセッサ コアです。このプロセッサは、消費者、医療、産業、自動車、通信インフラストラクチャ市場など、さまざまな分野のさまざまな要件を満たしています。それは非常に構成可能であるため、FPGA 内の組み込みプロセッサまたはマイクロコントローラとして使用され、それ以外の場合は ARM のコプロセッサのように使用されます。ここで質問です。FPGA とは何ですか?

“単極スイッチと双極 ”