この投稿では、論理ゲートとは何か、そしてその動作について包括的に理解します。基本的な定義、シンボル、真理値表、マルチ入力ゲートを見ていきます。また、トランジスタベースのゲート等価物を構築し、最後に、関連するさまざまなCMOSICの概要を説明します。

論理ゲートとは

電子回路の論理ゲートは、ブール関数で表される物理単位として表すことができます。

言い換えると、論理ゲートは、単一または複数のバイナリ入力を使用して論理関数を実行し、単一のバイナリ出力を生成するように設計されています。

電子論理ゲートは、基本的に、明確に定義されたスイッチングパターンを持つオン/オフスイッチのように機能するダイオードやトランジスタなどの半導体ブロックまたは要素を使用して構成および実装されます。論理ゲートは、ブール関数の合成を容易に可能にするようにゲートのカスケードを容易にし、すべてのブール論理の物理モデルを作成することを可能にします。これにより、ブール論理を使用して書き込み可能なアルゴリズムと数学がさらに有効になります。

論理回路は、マルチプレクサ、レジスタ、算術論理演算装置(ALU)、コンピュータメモリ、さらにはマイクロプロセッサの範囲で、数億もの論理ゲートを含む半導体要素を使用する場合があります。今日の実装では、主に電界効果トランジスタ(FET)が論理ゲートの製造に使用されており、その良い例が金属-酸化物-半導体電界効果トランジスタまたはMOSFETです。

ロジックANDゲートからチュートリアルを始めましょう。

ロジック「AND」ゲートとは何ですか?

これは電子ゲートであり、ANDゲートのすべての入力が「high」または「1」または「true」または「」の場合、出力が「high」または「1」または「true」になるか、「正の信号」を出力します。正の信号」。

例:入力数が「n」のANDゲートで、すべての入力が「ハイ」の場合、出力は「ハイ」になります。 1つの入力が「LOW」または「0」または「false」または「負の信号」であっても、出力は「LOW」または「0」または「false」になるか、「負の信号」を出力します。

注意:

「高」、「1」、「正の信号」、「真」という用語は基本的に同じです(正の信号はバッテリーまたは電源の正の信号です)。

「LOW」、「0」、「負の信号」、「false」という用語は基本的に同じです(負の信号はバッテリーまたは電源の負の信号です)。

ロジックANDゲート記号の図:

ここで、「A」と「B」は2つの入力であり、「Y」は出力されます。

論理ANDゲートのブール式:出力「Y」は、2つの入力「A」と「B」の乗算です。 (A.B)= Y。

ブール乗算はドット(。)で示されます。

「A」が「1」で「B」が「1」の場合、出力は(A.B)= 1 x 1 =「1」または「高」です。

「A」が「0」で「B」が「1」の場合、出力は(A.B)= 0 x 1 =「0」または「低」です。

「A」が「1」で「B」が「0」の場合、出力は(A.B)= 1 x 0 =「0」または「低」です。

「A」が「0」で「B」が「0」の場合、出力は(A.B)= 0 x 0 =「0」または「低」です。

上記の条件は、真理値表で簡略化されています。

真理値表(2つの入力):

| A(入力) | B(入力) | Y(出力) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3入力「AND」ゲート:

3入力ANDゲートの図:

論理ANDゲートには、「n」個の入力を含めることができます。つまり、3つ以上の入力を含めることができます(論理ANDゲートには、少なくとも2つの入力があり、常に1つの出力があります)。

3入力ANDゲートの場合、ブール方程式は次のようになります。(A.B.C)= Y、4入力以上の場合も同様です。

3入力ロジックANDゲートの真理値表:

| A(入力) | B(入力) | C(入力) | Y(出力) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

マルチ入力ロジックとゲート:

市販のロジックANDゲートは、2、3、および4入力でのみ使用できます。入力が4つを超える場合は、ゲートをカスケード接続する必要があります。

次のように2つの入力ANDゲートをカスケード接続することにより、6つの入力ロジックANDゲートを持つことができます。

これで、上記の回路のブール方程式はY =(A.B)。(C.D)。(E.F)になります。

それでも、上記のすべての論理規則が上記の回路に適用されます。

上記の6つの入力ANDゲートから5つの入力のみを使用する場合は、任意の1つのピンにプルアップ抵抗を接続すると、5つの入力ANDゲートになります。

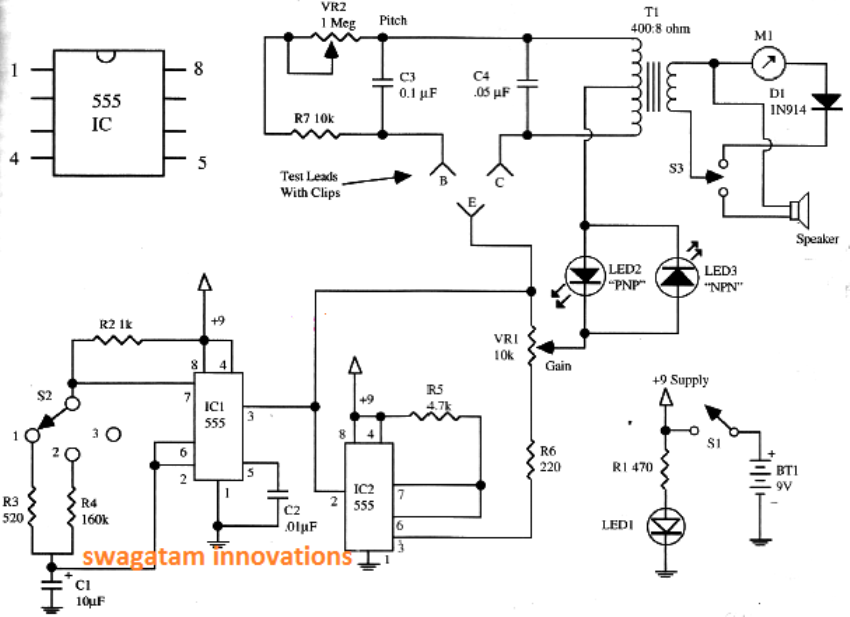

トランジスタベースの2入力ロジックANDゲート:

論理ANDゲートがどのように機能するかがわかったので、2つのNPNトランジスタを使用して2入力ANDゲートを構築しましょう。ロジックICはほぼ同じように構成されています。

2つのトランジスタとゲートの回路図:

出力「Y」でLEDを接続できます。出力が高い場合、LEDが点灯します(「Y」のLED + Ve端子、330オームの抵抗、GNDに対して負)。

2つのトランジスタのベースにハイ信号を印加すると、両方のトランジスタがオンになり、+ 5V信号がT2のエミッタで利用可能になるため、出力がハイになります。

トランジスタのいずれかがオフの場合、T2のエミッタで正の電圧は利用できませんが、1Kのプルダウン抵抗により、出力で負の電圧が利用できるため、出力はローと呼ばれます。

これで、独自のロジックANDゲートを構築する方法がわかりました。

クワッドANDゲートIC7408:

市場からロジックANDゲートを購入したい場合は、上記の構成になります。

14本のピンがあり、ピン#7とピン#14はそれぞれGNDとVccです。 5Vで動作します。

伝播遅延:

伝搬遅延は、出力がLOWからHIGHに、またはその逆に変化するのにかかる時間です。

LOWからHIGHへの伝搬遅延は27ナノ秒です。

HIGHからLOWへの伝搬遅延は19ナノ秒です。

その他の一般的に利用可能な「AND」ゲートIC:

•74LS08クワッド2入力

•74LS11トリプル3入力

•74LS21デュアル4入力

•CD4081クワッド2入力

•CD4073トリプル3入力

•CD4082デュアル4入力

詳細については、上記のICのデータシートをいつでも参照できます。

ロジック「排他的NOR」ゲート機能

この投稿では、ロジック「Ex-NOR」ゲートまたはExclusive-NORゲートについて説明します。基本的な定義、記号、真理値表、Ex-NOR等価回路、Ex-NORの実現を使用して見ていきます。 論理NANDゲート 最後に、クワッド2入力Ex-ORゲートIC74266の概要を説明します。

「ExclusiveNOR」ゲートとは何ですか?

これは電子ゲートであり、入力が偶数の論理「1」(または「真」または「高」または「」の場合、出力が「ハイ」または「1」または「真」になるか、「正の信号」を出力します。正の信号」)。

例:入力が「n」個の排他的NORゲートを、入力が2、4、または6個の入力(偶数個の入力「1」)の論理「HIGH」である場合、出力は「HIGH」になります。

入力ピンに論理「ハイ」を適用しない場合(つまり、論理「HIGH」の数がゼロですべての論理「LOW」)が適用されない場合でも、「ゼロ」は出力が「HIGH」になる偶数です。

適用される論理「1」の数がODDの場合、出力は「LOW」(または「0」または「false」または「負の信号」)になります。

これは、入力が奇数の論理「1」の場合に出力が「HIGH」になる論理「排他的論理和」ゲートの反対です。

注意:

「高」、「1」、「正の信号」、「真」という用語は基本的に同じです(正の信号はバッテリーまたは電源の正の信号です)。

「LOW」、「0」、「負の信号」、「false」という用語は基本的に同じです(負の信号はバッテリーまたは電源の負の信号です)。

ロジック「ExclusiveNOR」ゲートの図:

「排他的NOR」ゲート等価回路:

上記は論理Ex-NORの等価回路であり、基本的に論理「排他的論理和」ゲートと論理「NOT」ゲートを組み合わせたものです。

ここで、「A」と「B」は2つの入力であり、「Y」は出力されます。

論理Ex-NORゲートのブール式:Y =(AB)̅+ AB。

「A」が「1」で「B」が「1」の場合、出力は((AB)̅+ AB)= 0 + 1 =「1」または「HIGH」になります。

「A」が「0」で「B」が「1」の場合、出力は((AB)̅+ AB)= 0 + 0 =「0」または「LOW」になります。

「A」が「1」で「B」が「0」の場合、出力は((AB)̅+ AB)= 0 + 0 =「0」または「LOW」になります。

「A」が「0」で「B」が「0」の場合、出力は((AB)̅+ AB)= 1 + 1 =「1」または「HIGH」になります。

上記の条件は、真理値表で簡略化されています。

真理値表(2つの入力):

| A(入力) | B(入力) | Y(出力) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3入力専用NORゲート:

3入力Ex-NORゲートの図:

3入力ロジックEX-ORゲートの真理値表:

| A(入力) | B(入力) | C(入力) | Y(出力) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

3入力Ex-NORゲートの場合、ブール方程式は次のようになります。A̅(BC)̅+ABC̅+AB̅C+A̅BC。

論理「Ex-NOR」ゲートは基本的な論理ゲートではなく、異なる論理ゲートの組み合わせです。 Ex-NORゲートは、論理「OR」ゲート、論理「AND」ゲート、および論理「NAND」ゲートを使用して次のように実現できます。

「ExclusiveNOR」ゲートの等価回路:

上記の設計には大きな欠点があり、1つのEx-NORゲートを作成するには3つの異なる論理ゲートが必要です。しかし、論理「NAND」ゲートのみでEx-NORゲートを実装することでこの問題を克服できます。これは、製造するのにも経済的です。

NANDゲートを使用した専用NORゲート:

排他的NORゲートは、算術演算、バイナリ加算器、バイナリ減算、パリティチェッカーなどの複雑なコンピューティングタスクを実行するために使用され、デジタルコンパレータとして使用されます。

ロジックエクスクルーシブ-NORゲートIC74266:

ロジックEx-NORゲートを市場から購入したい場合は、上記のDIP構成になります。

14本のピンがあり、ピン#7とピン#14はそれぞれGNDとVccです。 5Vで動作します。

伝播遅延:

伝搬遅延は、入力を行った後、出力がLOWからHIGHに、またはその逆に変化するのにかかる時間です。

LOWからHIGHへの伝搬遅延は23ナノ秒です。

HIGHからLOWへの伝搬遅延は23ナノ秒です。

一般的に入手可能な「EX-NOR」ゲートIC:

74LS266クワッド2入力

CD4077クワッド2入力

NANDゲートのしくみ

以下の説明では、デジタル論理NANDゲートについて説明します。基本的な定義、記号、真理値表、マルチ入力NANDゲート、トランジスタベースの2入力NANDゲート、NANDゲートのみを使用したさまざまな論理ゲートを構築し、最後にNANDゲートの概要を説明します。 IC7400。

ロジック「NAND」ゲートとは何ですか?

これは電子ゲートであり、NANDゲートのすべての入力が「ハイ」または「1」または「真」または「」の場合、出力が「LOW」または「0」または「false」になるか、「負の信号」を出力します。正の信号」。

例:入力数が「n」のNANDゲートを考えてみましょう。すべての入力が「ハイ」の場合、出力は「ロー」になります。 1つの入力が「LOW」または「0」または「false」または「負の信号」であっても、出力は「HIGH」または「1」または「true」になるか、「正の信号」を出力します。

注意:

「高」、「1」、「正の信号」、「真」という用語は基本的に同じです(正の信号はバッテリーまたは電源の正の信号です)。

「LOW」、「0」、「負の信号」、「false」という用語は基本的に同じです(負の信号はバッテリーまたは電源の負の信号です)。

ロジックNANDゲートシンボルの図:

ここで、「A」と「B」は2つの入力であり、「Y」は出力されます。

この記号は、反転「o」の付いた「AND」ゲートです。

論理「NAND」ゲート等価回路:

論理NANDゲートは、論理「AND」ゲートと論理「NOT」ゲートの組み合わせです。

論理NANDゲートのブール式:出力「Y」は、2つの入力「A」と「B」の相補乗算です。 Y =((A.B)̅)

ブール乗算はドット(。)で示され、相補(反転)は文字上のバー(-)で表されます。

「A」が「1」で「B」が「1」の場合、出力は((A.B)̅)=(1 x 1)̅=「0」または「LOW」になります。

「A」が「0」で「B」が「1」の場合、出力は((A.B)̅)=(0 x 1)̅=「1」または「HIGH」になります。

「A」が「1」で「B」が「0」の場合、出力は((A.B)̅)=(1 x 0)̅=「1」または「HIGH」になります。

「A」が「0」で「B」が「0」の場合、出力は((A.B)̅)=(0 x 0)̅=「1」または「HIGH」になります。

上記の条件は、真理値表で簡略化されています。

真理値表(2つの入力):

| A(入力) | B(入力) | Y(出力) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

3入力「NAND」ゲート:

3入力NANDゲートの図:

論理NANDゲートは、「n」個の入力を持つことができます。つまり、3つ以上の入力を持つことができます。

(論理NANDゲートには、少なくとも2つの入力と常に1つの出力があります)。

3入力NANDゲートの場合、ブール方程式は次のようになります。((A.B.C)̅)= Y、4入力以上の場合も同様です。

真理値表3入力ロジックNANDゲートの場合:

| A(入力) | B(入力) | C(入力) | Y(出力) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

マルチ入力ロジックNANDゲート:

市販のロジックNANDゲートは、2、3、および4入力でのみ使用できます。入力が4つを超える場合は、ゲートをカスケード接続する必要があります。

たとえば、次のように5つの2つの入力NANDゲートをカスケード接続することにより、4つの入力論理NANDゲートを持つことができます。

これで、上記の回路のブール方程式はY =((A.B.C.D)̅)になります。

それでも、上記のすべての論理規則が上記の回路に適用されます。

上記の4入力NANDゲートから3入力のみを使用する場合は、プルアップ抵抗を任意の1つのピンに接続すると、3入力NANDゲートになります。

トランジスタベースの2入力ロジックNANDゲート:

論理NANDゲートがどのように機能するかがわかったので、2つを使用して2入力NANDゲートを構築しましょう。

NPNトランジスタ。ロジックICはほぼ同じように構成されています。

2つのトランジスタNANDゲートの回路図:

出力「Y」では、出力が高い場合にLEDを接続でき、LEDが点灯します(「Y」のLED + Ve端子、330オームの抵抗、GNDに対して負)。

2つのトランジスタのベースにHigh信号を印加すると、両方のトランジスタがオンになり、T1のコレクタでグランド信号が利用できるようになるため、出力が「LOW」になります。

トランジスタのいずれかがオフの場合、つまり「LOW」信号をベースに適用すると、T1のコレクタでグランド信号は利用できませんが、1Kのプルアップ抵抗により、出力で正の信号が利用可能になり、出力がターンします。 '高い'。

これで、独自の論理NANDゲートを構築する方法がわかりました。

NANDゲートを使用したさまざまな論理ゲート:

NANDゲートは、この単一のゲートで任意のブール論理を作成できるため、「ユニバーサル論理ゲート」とも呼ばれます。これは、論理機能の異なるICを製造する場合の利点であり、単一のゲートを製造することは経済的です。

上記の回路図では、3種類のゲートのみが示されていますが、任意のブール論理を作成できます。

“合計計算機のkマップ積 ”

クワッドNANDゲートIC7400:

市場から論理NANDゲートを購入したい場合は、上記のDIP構成になります。

14本のピンがあり、ピン#7とピン#14はそれぞれGNDとVccです。 5Vで動作します。

伝播遅延:

伝搬遅延は、入力を行った後、出力がLOWからHIGHに、またはその逆に変化するのにかかる時間です。

LOWからHIGHへの伝搬遅延は22ナノ秒です。

HIGHからLOWへの伝搬遅延は15ナノ秒です。

利用可能な他のいくつかのNANDゲートICがあります:

- 74LS00クワッド2入力

- 74LS10トリプル3入力

- 74LS20デュアル4入力

- 74LS30シングル8入力

- CD4011クワッド2入力

- CD4023トリプル3入力

- CD4012デュアル4入力

NORゲートのしくみ

ここでは、デジタル論理NORゲートについて説明します。基本的な定義、シンボル、真理値表、マルチ入力NORゲート、トランジスタベースの2入力NORゲート、NORゲートのみを使用したさまざまな論理ゲートを構築し、最後にNORゲートの概要を説明します。 IC7402。

ロジック「NOR」ゲートとは何ですか?

これは電子ゲートであり、NORゲートのすべての入力が「LOW」または「0」または「false」または「」の場合、出力が「HIGH」または「1」または「true」になるか、「正の信号」を出力します。負の信号」。

例:入力数が「n」のNORゲートを言うと、すべての入力が「LOW」の場合、出力は「HIGH」になります。 1つの入力が「HIGH」または「1」または「true」または「正の信号」であっても、出力は「LOW」または「0」または「false」になるか、「負の信号」を出力します。

注意:

「高」、「1」、「正の信号」、「真」という用語は基本的に同じです(正の信号はバッテリーまたは電源の正の信号です)。

「LOW」、「0」、「負の信号」、「false」という用語は基本的に同じです(負の信号はバッテリーまたは電源の負の信号です)。

ロジックNORゲートシンボルの図:

ここで、「A」と「B」は2つの入力であり、「Y」は出力されます。

この記号は、反転「o」の付いた「OR」ゲートです。

論理「NOR」ゲート等価回路:

論理NORゲートは、論理「OR」ゲートと論理「NOT」ゲートの組み合わせです。

論理NORゲートのブール式:出力「Y」は、2つの入力「A」と「B」の補完的な加算です。 Y =((A + B)̅)

ブール加算は(+)で示され、補完(反転)は文字上のバー(-)で表されます。

「A」が「1」で「B」が「1」の場合、出力は((A + B)̅)=(1+ 1)̅=「0」または「LOW」になります。

「A」が「0」で「B」が「1」の場合、出力は((A + B)̅)=(0+ 1)̅=「0」または「LOW」になります。

「A」が「1」で「B」が「0」の場合、出力は((A + B)̅)=(1+ 0)̅=「0」または「LOW」になります。

「A」が「0」で「B」が「0」の場合、出力は((A + B)̅)=(0+ 0)̅=「1」または「HIGH」になります。

上記の条件は、真理値表で簡略化されています。

真理値表(2つの入力):

| A(入力) | B(入力) | Y(出力) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

3入力「NOR」ゲート:

3入力NORゲートの図:

論理NORゲートは、「n」個の入力を持つことができます。つまり、3つ以上の入力を持つことができます(論理NORゲートには、少なくとも2つの入力があり、常に1つの出力があります)。

3入力NORゲートの場合、ブール方程式は次のようになります。((A + B + C)̅)= Y、4入力以上の場合も同様です。

3入力ロジックNORゲートの真理値表:

| A(入力) | B(入力) | C(入力) | Y(出力) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

マルチ入力ロジックNORゲート:

市販のロジックNORゲートは、2、3、および4入力でのみ使用できます。入力が4つを超える場合は、ゲートをカスケード接続する必要があります。

たとえば、次のように5つの2つの入力NORゲートをカスケード接続することにより、4つの入力ロジックNORゲートを持つことができます。

これで、上記の回路のブール方程式はY =((A + B + C + D)̅)になります。

それでも、上記のすべての論理規則が上記の回路に適用されます。

上記の4入力NORゲートから3入力のみを使用する場合は、プルダウン抵抗をピンのいずれかに接続すると、3入力NORゲートになります。

トランジスタベースの2入力ロジックNORゲート:

論理NORゲートがどのように機能するかがわかったので、2つのNPNトランジスタを使用して2入力NORゲートを作成しましょう。ロジックICはほぼ同じように構成されています。

2つのトランジスタNORゲートの回路図:

出力「Y」では、出力が高い場合にLEDを接続でき、LEDが点灯します(「Y」のLED + Ve端子、330オームの抵抗、GNDに対して負)。

2つのトランジスタのベースに「HIGH」信号を印加すると、両方のトランジスタがオンになり、T1とT2のコレクタでグランド信号が利用できるようになるため、出力が「LOW」になります。

いずれかのトランジスタに「HIGH」を適用しても、出力で負の信号が利用可能になり、出力が「LOW」になります。

2つのトランジスタのベースに「LOW」信号を印加すると、両方ともオフになりますが、プルアップ抵抗のために出力は「HIGH」になります。

これで、独自のロジックNORゲートを構築する方法がわかりました。

NORゲートを使用したさまざまな論理ゲート:

注:NANDとNORは、ユニバーサルゲートとも呼ばれる2つのゲートです。

NORゲートは、この単一のゲートで任意のブール論理を作成できるため、「ユニバーサル論理ゲート」でもあります。これは、異なる論理機能を備えたICを製造する場合の利点であり、単一のゲートを製造することは経済的です。これはNANDゲートでも同じです。

上記の回路図では、3種類のゲートのみが示されていますが、任意のブール論理を作成できます。

クワッドNORゲートIC7402:

市場から論理NORゲートを購入したい場合は、上記のDIP構成になります。

14本のピンがあり、ピン#7とピン#14はそれぞれGNDとVccです。 5Vで動作します。

伝播遅延:

伝搬遅延は、入力を行った後、出力がLOWからHIGHに、またはその逆に変化するのにかかる時間です。

LOWからHIGHへの伝搬遅延は22ナノ秒です。

HIGHからLOWへの伝搬遅延は15ナノ秒です。

利用可能な他のいくつかのNORゲートICがあります:

- 74LS02クワッド2入力

- 74LS27トリプル3入力

- 74LS260デュアル4入力

- CD4001クワッド2入力

- CD4025トリプル3入力

- CD4002デュアル4入力

ロジックNOTゲート

この投稿では、論理「NOT」ゲートについて説明します。その基本的な定義、記号、真理値表、NANDおよびNORゲートの同等物、シュミットインバーター、シュミットNOTゲート発振器、トランジスタを使用したNOTゲートについて学習し、最後にロジックNOTゲートインバータIC7404について見ていきます。

デジタルインバーターとも呼ばれる論理NOTゲートの詳細を検討する前に、家庭やオフィスの太陽光発電やバックアップ電源に使用されている「パワーインバーター」と混同しないでください。

ロジック「NOT」ゲートとは何ですか?

これは、出力が入力を補完する単一の入力および単一の出力論理ゲートです。

上記の定義は、入力が「HIGH」または「1」または「true」または「正の信号」である場合、出力は「LOW」または「0」または「false」または「負の信号」になることを示しています。

入力が「LOW」または「0」または「false」または「負の信号」の場合、出力は「HIGH」または「1」または「true」または「正の信号」に反転されます。

注意:

「高」、「1」、「正の信号」、「真」という用語は基本的に同じです(正の信号はバッテリーまたは電源の正の信号です)。

「LOW」、「0」、「負の信号」、「false」という用語は基本的に同じです(負の信号はバッテリーまたは電源の負の信号です)。

ロジックNOTゲートの図:

「A」が入力で「Y」が出力であると仮定します。論理NOTゲートのブール方程式は次のとおりです。Ā= Y。

この方程式は、出力が入力の反転であることを示しています。

論理NOTゲートの真理値表:

| に (入力) | Y (出力) |

| 0 | 1 |

| 1 | 0 |

notゲートは、常に単一の入力を持ち(そして、常に単一の出力を持ちます)、意思決定デバイスとして分類されます。三角形の先端にある「o」記号は、補完または反転を表します。

この「o」記号は、論理「NOT」ゲートに限定されるだけでなく、任意の論理ゲートまたは任意のデジタル回路で使用できます。 「o」が入力にある場合、これは入力がアクティブ-ローであることを示します。

Active-Low:「LOW」入力が与えられると、出力がアクティブになります(トランジスタ、LED、またはリレーなどをアクティブにします)。

NANDおよびNORゲートと同等:

「NOT」ゲートは、すべての入力ピンを結合することにより、論理「NAND」および論理「NOR」ゲートを使用して構築できます。これは、3、4、およびそれ以上の入力ピンを持つゲートに適用されます。

トランジスタベースのロジック「NOT」ゲート:

論理「NOT」は、NPNトランジスタと1K抵抗で構成できます。トランジスタのベースに「HIGH」信号を印加すると、グランドがトランジスタのコレクタに接続されるため、出力が「LOW」になります。

トランジスタのベースに「LOW」信号を印加すると、トランジスタはオフのままでグランドに接続されませんが、出力はVccに接続されたプルアップ抵抗によって「HIGH」にプルされます。したがって、トランジスタを使用して論理「NOT」ゲートを作成できます。

シュミットインバーター:

シュミットインバーターの利用と機能を説明するために、自動バッテリー充電器でこの概念を探求します。リチウムイオン電池の充電手順の例を見てみましょう。

3.7 Vリチウムイオンバッテリーは、バッテリーが3Vから3.2Vに達すると充電されます。充電中はバッテリー電圧が徐々に上昇し、4.2 Vでバッテリーを遮断する必要があります。充電後、バッテリーの開回路電圧は約4.0V低下します。 。

電圧センサーがカットオフ制限を測定し、リレーをトリガーして充電を停止します。しかし、電圧が4.2Vを下回ると、充電器は充電されていないことを検出し、4.2Vまで充電を開始してカットオフします。再び、バッテリー電圧は4.0Vに下がり、充電を再開し、この狂気が何度も繰り返されます。

これにより、バッテリーがすぐに停止します。この問題を克服するには、バッテリーが3 V〜3.2 Vに低下するまでバッテリーが充電を開始しないように、より低いしきい値レベルまたは「LTV」が必要です。上限しきい値電圧または「UTV」はこの例では4.2Vです。

シュミットインバータは、電圧が上限しきい値電圧を超えると出力状態を切り替え、入力が下限しきい値電圧に達するまで同じままになります。

同様に、入力が下限しきい値電圧を超えると、入力が上限しきい値電圧に達するまで出力は同じままです。

LTVとUTVの間で状態が変わることはありません。

これにより、ON / OFFがよりスムーズになり、不要な発振が除去され、回路の電気ノイズに対する耐性も高まります。

シュミットNOTゲートオシレーター:

上記の回路は、33%のデューティサイクルで方形波を生成する発振器です。最初、コンデンサは放電状態にあり、接地信号はNOTゲートの入力で利用可能になります。

出力は正になり、抵抗「R」を介してコンデンサを充電します。コンデンサは、インバータの上限しきい値電圧まで充電されて状態が変化します。出力は負の信号になり、コンデンサは、コンデンサ電圧に達するまで抵抗「R」を介して放電を開始します。下限しきい値レベルで状態が変化すると、出力が正になり、コンデンサが充電されます。

このサイクルは、電源が回路に供給されている限り繰り返されます。

上記の発振器の周波数は計算できます:F = 680 / RC

ここで、Fは周波数です。

Rはオーム単位の抵抗です。

Cはファラッド単位の静電容量です。

方形波コンバーター:

上記の回路は正弦波信号を方形波に変換しますが、実際には任意のアナログ波を方形波に変換できます。

2つの抵抗R1とR2は分圧器として機能し、これはバイアスポイントを取得するために使用され、コンデンサはDC信号をブロックします。

入力信号が上限しきい値レベルを超えるか、下限しきい値レベルを下回ると、出力が変わります。

信号に応じてLOWまたはHIGHになり、方形波が生成されます。

IC 7404 NOTゲートインバーター:

IC 7404は、最も一般的に使用されているロジックNOTゲートICの1つです。 14個のピンがあり、ピン#7はグランドで、ピン#14はVccです。動作電圧は4.5Vから5Vです。

伝播遅延:

伝搬遅延は、入力を与えた後、ゲートが出力を処理するのにかかる時間です。

論理的には、「NOT」ゲートは、状態をHIGHからLOWに、またはその逆に変更するのに約22ナノ秒かかります。

他にもいくつかのロジック「NOTゲートIC:

•74LS04六角反転NOTゲート

•74LS14六角シュミット反転NOTゲート

•74LS1004六角反転ドライバー

•CD4009六角反転NOTゲート

•CD4069六角反転NOTゲート

ORゲートのしくみ

それでは、デジタルロジックORゲートについて見ていきましょう。基本的な定義、シンボル、真理値表、マルチ入力ORゲートを見て、トランジスタベースの2入力ORゲートを構築し、最後にORゲートIC7432の概要を説明します。

ロジック「OR」ゲートとは何ですか?

これは電子ゲートであり、ORゲートのすべての入力が「LOW」または「0」または「false」または「」の場合、出力が「LOW」または「0」または「false」になるか、「負の信号」を出力します。負の信号」。

例:入力数が「n」のORゲートを言うと、すべての入力が「LOW」の場合、出力は「LOW」になります。 1つの入力が「HIGH」または「1」または「true」または「正信号」であっても、出力は「HIGH」または「1」または「true」になるか、「正信号」を出力します。

注意:

「高」、「1」、「正の信号」、「真」という用語は基本的に同じです(正の信号はバッテリーまたは電源の正の信号です)。

「LOW」、「0」、「負の信号」、「false」という用語は基本的に同じです(負の信号はバッテリーまたは電源の負の信号です)。

ロジックORゲートシンボルの図:

ここで、「A」と「B」は2つの入力であり、「Y」は出力されます。

論理ORゲートのブール式:出力「Y」は、2つの入力「A」と「B」の加算です(A + B)= Y。

ブール加算は(+)で示されます

「A」が「1」で「B」が「1」の場合、出力は(A + B)= 1 + 1 =「1」または「高」になります。

「A」が「0」で「B」が「1」の場合、出力は(A + B)= 0 + 1 =「1」または「高」になります。

「A」が「1」で「B」が「0」の場合、出力は(A + B)= 1 + 0 =「1」または「高」になります。

「A」が「0」で「B」が「0」の場合、出力は(A + B)= 0 + 0 =「0」または「低」です。

上記の条件は、真理値表で簡略化されています。

真理値表(2つの入力):

| A(入力) | B(入力) | Y(出力) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

3入力「OR」ゲート:

3入力ORゲートの図:

論理ORゲートは、「n」個の入力を持つことができます。つまり、3つ以上の入力を持つことができます(論理ORゲートには、少なくとも2つの入力があり、常に1つの出力があります)。

3入力論理ORゲートの場合、ブール方程式は次のようになります。(A + B + C)= Y、4入力以上の場合も同様です。

3入力論理ORゲートの真理値表:

| A(入力) | B(入力) | C(入力) | Y(出力) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

マルチ入力ロジックORゲート:

市販のロジックORゲートは、2、3、および4入力でのみ使用できます。入力が4つを超える場合は、ゲートをカスケード接続する必要があります。

次のように2つの入力ORゲートをカスケード接続することにより、6つの入力ロジックORゲートを持つことができます。

これで、上記の回路のブール方程式はY =(A + B)+(C + D)+(E + F)になります。

それでも、上記のすべての論理規則が上記の回路に適用されます。

上記の6入力ORゲートから5入力のみを使用する場合は、任意の1つのピンにプルダウン抵抗を接続でき、5入力ORゲートになります。

トランジスタベースの2入力ロジックORゲート:

論理ORゲートがどのように機能するかがわかったので、2つのNPNトランジスタを使用して2入力ORゲートを構築しましょう。ロジックICはほぼ同じように構成されています。

2つのトランジスタORゲートの回路図:

出力「Y」でLEDを接続できます。出力が高い場合、LEDが点灯します(「Y」のLED + Ve端子、330オームの抵抗、GNDに対して負)。

2つのトランジスタのベースにLOW信号を印加すると、両方のトランジスタがオフになり、1kプルダウン抵抗を介してT2 / T1のエミッタでグランド信号が利用できるようになるため、出力がLOWになります。

トランジスタのいずれかがオンの場合、T2 / T1のエミッタで正の電圧が利用可能になるため、出力はHIGHになります。

これで、独自のロジックORゲートを構築する方法がわかりました。

クワッドORゲートIC7432:

市場からロジックORゲートを購入したい場合は、上記の構成になります。

14本のピンがあり、ピン#7とピン#14はそれぞれGNDとVccです。 5Vで動作します。

伝播遅延:

伝搬遅延は、出力がLOWからHIGHに、またはその逆に変化するのにかかる時間です。

LOWからHIGHへの伝搬遅延は、摂氏25度で7.4ナノ秒です。

HIGHからLOWへの伝搬遅延は、摂氏25度で7.7ナノ秒です。

•74LS32クワッド2入力

•CD4071クワッド2入力

•CD4075トリプル3入力

•CD4072デュアル4入力

ロジックエクスクルーシブ–ORゲート

この投稿では、論理XORゲートまたは排他的論理和ゲートについて説明します。基本的な定義、記号、真理値表、XOR等価回路、論理NANDゲートを使用したXORの実現について見ていきます。最後に、クアッド2入力Ex-ORゲートIC7486の概要について説明します。

以前の投稿では、3つの基本的な論理ゲート「AND」、「OR」、「NOT」について学びました。また、これら3つの基本ゲートを使用して、2つの新しい論理ゲート「NAND」と「NOR」を構築できることも学びました。

これら2つは基本的なゲートではありませんが、さらに2つの論理ゲートがありますが、他の論理ゲートの組み合わせによって構築され、そのブール方程式は非常に重要で非常に有用であるため、別個の論理ゲートと見なされます。

これらの2つの論理ゲートは、「排他的論理和」ゲートと「排他的論理和」です。この投稿では、論理排他的論理和ゲートについてのみ説明します。

「排他的論理和」ゲートとは何ですか?

これは電子ゲートであり、2つの論理入力が互いに異なる場合に出力が「ハイ」または「1」または「真」になるか「正の信号」を出力します(これは2つの2入力にのみ適用されますEx -ORゲート)。

例:「2つの」入力を持つ排他的論理和ゲートを考えます。入力ピンAの1つが「HIGH」で、入力ピンBが「LOW」の場合、出力は「HIGH」または「1」または「true」になります。 「ポジティブシグナル」。

両方の入力が同じ論理レベルの場合、つまり両方のピンが「HIGH」または両方のピンが「LOW」の場合、出力は「LOW」または「0」または「false」または「負の信号」に変わります。

注意:

「高」、「1」、「正の信号」、「真」という用語は基本的に同じです(正の信号はバッテリーまたは電源の正の信号です)。

「LOW」、「0」、「負の信号」、「false」という用語は基本的に同じです(負の信号はバッテリーまたは電源の負の信号です)。

ロジック排他的ORゲートの図:

ここで、「A」と「B」は2つの入力であり、「Y」は出力されます。

論理Ex-ORゲートのブール式:Y =(A.)̅B+A.B̅

「A」が「1」で「B」が「1」の場合、出力は(A̅.B+A.B̅)= 0 x 1 + 1 x 0 =「1」または「LOW」になります。

「A」が「0」で「B」が「1」の場合、出力は(A̅.B+A.B̅)= 1 x 1 + 0 x 0 =「1」または「HIGH」になります。

「A」が「1」で「B」が「0」の場合、出力は(A̅.B+A.B̅)= 0 x 0 + 1 x 1 =「1」または「HIGH」になります。

「A」が「0」で「B」が「0」の場合、出力は(A̅.B+A.B̅)= 1 x 0 + 0 x 1 =「0」または「低」になります。

上記の条件は、真理値表で簡略化されています。

真理値表(2つの入力):

| A(入力) | B(入力) | Y(出力) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

上記の2つの入力ロジックEx-ORゲートでは、2つの入力が異なる場合、つまり「1」と「0」の場合、出力は「HIGH」になります。ただし、3つ以上の入力ロジックEx-ORを使用する場合、または一般にEx-ORの出力は、奇数のロジック「HIGH」がゲートに適用された場合にのみ「HIGH」になります。

例:3つの入力Ex-ORゲートがある場合、論理「HIGH」を1つの入力(奇数の論理「1」)にのみ適用すると、出力は「HIGH」になります。ロジック「HIGH」を2つの入力(これは偶数のロジック「1」)に適用すると、出力は「LOW」になります。

3入力専用ORゲート:

3入力EX-ORゲートの図:

3入力ロジックEX-ORゲートの真理値表:

| A(入力) | B(入力) | C(入力) | Y(出力) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

3入力Ex-ORゲートの場合、ブール方程式は次のようになります。A(BC)̅+A̅BC̅+(AB)̅C+ ABC

前に説明したように、論理「Ex-OR」ゲートは基本的な論理ゲートではなく、異なる論理ゲートの組み合わせです。 Ex-ORゲートは、論理「OR」ゲート、論理「AND」ゲート、および論理「NAND」ゲートを使用して、次のように実現できます。

「排他的論理和」ゲートの等価回路:

上記の設計には大きな欠点があり、1つのEx-ORゲートを作成するには3つの異なる論理ゲートが必要です。しかし、論理NANDゲートのみでEx-ORゲートを実装することでこの問題を克服できます。これは、製造するのにも経済的です。

NANDゲートを使用した排他的ORゲート:

排他的論理和ゲートは、算術演算、全加算器、半加算器などの複雑な計算タスクを実行するために使用され、実行機能を提供することもできます。

ロジック排他的論理和ゲートIC7486:

ロジックEx-ORゲートを市場から購入したい場合は、上記のDIP構成になります。

14本のピンがあり、ピン#7とピン#14はそれぞれGNDとVccです。 5Vで動作します。

伝播遅延:

伝搬遅延は、入力を行った後、出力がLOWからHIGHに、またはその逆に変化するのにかかる時間です。

LOWからHIGHへの伝搬遅延は23ナノ秒です。

HIGHからLOWへの伝搬遅延は17ナノ秒です。

一般的に入手可能な「EX-OR」ゲートIC:

- 74LS86クワッド2入力

- CD4030クワッド2入力

まだ質問がある場合は、上記の詳細な説明が、論理ゲートとは何か、論理ゲートがどのように機能するかについて理解するのに役立つことを願っています。コメント欄にご記入ください。すぐに返信があります。

前:コンデンサ漏れテスター回路–漏れのあるコンデンサをすばやく見つける 次へ:デジタルバッファ–動作、定義、真理値表、二重反転、ファンアウト