コンピュータが巨大で、設置するのに簡単に部屋のスペースが必要だった時代がありました。しかし、今日ではそれらは非常に進化しているため、ノートブックとしても簡単に持ち運ぶことができます。これを可能にした革新は、集積回路の概念でした。に 集積回路 、多数のアクティブおよび 受動素子 それらの相互接続とともに、通常は断面積が50 x50ミルの小さなシリコンウェーハ上に開発されます。このような回路の製造に続く基本的なプロセスには、エピタキシャル成長、マスクされた不純物拡散、酸化物成長、およびパターンを作成するためのフォトリソグラフィーを使用した酸化物エッチングが含まれます。

ウェーハ上のコンポーネントには、抵抗、トランジスタ、ダイオード、コンデンサなどが含まれます。IC上で製造するのに最も複雑な要素はトランジスタです。 トランジスタにはさまざまな種類があります CMOS、BJT、FETなど。要件に基づいて、ICに実装するトランジスタ技術のタイプを選択します。この記事では、の概念を理解しましょう。 CMOS製造 (または)CMOSとしてのトランジスタの製造。

CMOS製作

より少ない消費電力要件のために CMOSテクノロジー トランジスタの実装に使用されます。より高速な回路が必要な場合は、トランジスタを実装します。 IC使用 BJT 。の製作 CMOSトランジスタ ICは3つの異なる方法で実行できるためです。

n型拡散がp型基板上で行われる、またはp型拡散がn型基板上で行われるNウェル/ Pウェル技術。

ザ・ ツインウェルテクノロジー 、 どこ MOSFET およびPMOSトランジスタ 基板ではなく、エピタキシャル成長ベース上での同時拡散によってウェーハ上に現像されます。

シリコンオンインシュレータプロセス。基板としてシリコンを使用するのではなく、絶縁体材料を使用して速度とラッチアップの影響を受けやすくします。

N-ウェル/ P-ウェルテクノロジー

CMOSは両方を統合することで得られます MOSFETおよびPMOSトランジスタ 同じシリコンウェーハ上。 Nウェル技術では、n型ウェルはp型基板上に拡散しますが、Pウェル技術ではその逆です。

CMOS製造ステップ

ザ・ CMOS製造プロセス フロー Nウェル/ Pウェル技術を使用して製造されている間、20の基本的な製造ステップを使用して実施されます。

Nウェルを使用したCMOSの作成

ステップ1: まず、製造のベースとして基板を選択します。 Nウェルの場合、P型シリコン基板が選択されます。

基板

ステップ2–酸化: n型不純物の選択的拡散は、基板の汚染からウェーハの一部を保護するバリアとしてSiO2を使用して実現されます。 SiO二約1000の酸化チャンバー内で基板を高品質の酸素と水素にさらして行われる酸化プロセスによってレイアウトされます0c

酸化

ステップ3–フォトレジストの成長: 選択的エッチングを可能にするこの段階で、SiO2層はフォトリソグラフィープロセスにかけられます。このプロセスでは、ウェーハは感光乳剤の均一なフィルムでコーティングされます。

フォトレジストの成長

ステップ4–マスキング: このステップは、フォトリソグラフィープロセスの続きです。このステップでは、ステンシルを使用して、必要な開放パターンを作成します。このステンシルは、フォトレジストのマスクとして使用されます。基板は今露出されています 紫外線 マスクの露光領域の下に存在するフォトレジストが重合します。

フォトレジストのマスキング

ステップ5–未露光のフォトレジストの除去: トリクロロエチレンなどの化学薬品を使用してウェーハを現像することにより、マスクが除去され、フォトレジストの未露光領域が溶解される。

フォトレジストの除去

ステップ6–エッチング: ウェーハはフッ化水素酸のエッチング液に浸され、ドーパントが拡散される領域から酸化物が除去されます。

SiO2のエッチング

ステップ7–フォトレジスト層全体の除去: 間に エッチングプロセス 、フォトレジスト層によって保護されているSiO2の部分は影響を受けません。フォトレジストマスクは、化学溶剤(高温のH2SO4)で剥がされます。

フォトレジスト層の除去

ステップ8– Nウェルの形成: n型不純物は露出領域を介してp型基板に拡散し、Nウェルを形成します。

Nウェルの形成

ステップ9– SiO2の除去: フッ化水素酸を使用して、SiO2の層を除去します。

SiO2の除去

ステップ10–ポリシリコンの堆積: のゲートのずれ CMOSトランジスタ 回路に害を及ぼす可能性のある不要な静電容量につながる可能性があります。したがって、この「自己整合ゲートプロセス」を防ぐために、イオン注入を使用してソースとドレインを形成する前にゲート領域を形成する場合に適しています。

ポリシリコンの堆積

ポリシリコンは8000を超える高温に耐えることができるため、ゲートの形成に使用されます0cウェーハがソースとドレインの形成のためにアニーリング法にかけられたとき。ポリシリコンは、 化学蒸着プロセス ゲート酸化物の薄層の上。ポリシリコン層の下のこの薄いゲート酸化物は、ゲート領域の下でのさらなるドーピングを防ぎます。

ステップ11–ゲート領域の形成: ゲートの形成に必要な2つの領域を除いて MOSFETおよびPMOSトランジスタ ポリシリコンの残りの部分は取り除かれます。

ゲート領域の形成

ステップ12–酸化プロセス: 酸化層がウェーハ上に堆積され、これがさらにシールドとして機能します。 拡散およびメタライゼーションプロセス 。

酸化プロセス

ステップ13–マスキングと拡散: マスキングプロセスを使用してn型不純物の拡散領域を作成するために、小さなギャップが作成されます。

マスキング

拡散プロセスを使用して、NMOSの端子を形成するために3つのn +領域が開発されます。

N拡散

ステップ14–酸化物の除去: 酸化物層が剥ぎ取られます。

酸化物の除去

ステップ15– P型拡散: POMSの端子を形成するためのn型拡散と同様に、p型拡散が行われる。

P型拡散

ステップ16–厚いフィールド酸化物の敷設: 金属端子を形成する前に、厚い電界酸化物を配置して、端子が不要なウェーハの領域の保護層を形成します。

厚いフィールド酸化物層

ステップ17–メタライゼーション: このステップは、相互接続を提供できる金属端子の形成に使用されます。アルミニウムはウェーハ全体に広がっています。

メタライゼーション

ステップ18–余分な金属の除去: 余分な金属はウェーハから除去されます。

ステップ19–ターミナルの形成: 余分な金属の除去後に形成されたギャップには、相互接続用の端子が形成されます。

ターミナルの形成

ステップ20–端末名の割り当て: の端子に名前が割り当てられています MOSFETおよびPMOSトランジスタ 。

ターミナル名の割り当て

Pウェルテクノロジーを使用したCMOSの作成

pウェルプロセスはNウェルプロセスと似ていますが、ここではn型基板が使用され、p型拡散が実行される点が異なります。通常、簡単にするために、Nウェルプロセスが推奨されます。

CMOSのツインチューブ製造

ツインチューブプロセスを使用すると、PおよびNタイプのデバイスのゲインを制御できます。に含まれるさまざまな手順 CMOSの製造 ツインチューブ方式を使用 以下の通り

- 軽くドープされたn型またはp型基板が採用され、エピタキシャル層が使用されます。エピタキシャル層は、チップのラッチアップの問題を保護します。

- 測定された厚さと正確なドーパント濃度を備えた高純度シリコン層が成長します。

- PおよびNウェル用のチューブの形成。

- 拡散プロセス中の汚染から保護するための薄い酸化物構造。

- ソースとドレインは、イオン注入法を使用して形成されます。

- 金属接点用の部分を作るためにカットが行われます。

- 金属接点を描画するためにメタライゼーションが行われます

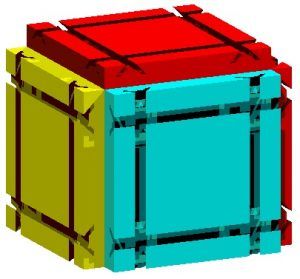

CMOSICレイアウト

の上面図 CMOSへ 製作とレイアウト 与えられます。ここでは、さまざまな金属接触とNウェル拡散をはっきりと見ることができます。

CMOSICレイアウト

したがって、これはすべてについてです CMOS製造技術 。 50ミル×50ミルの表面積の400チップに分割された1インチの正方形のウェーハを考えてみましょう。トランジスタの製造には50mil2の面積が必要です。したがって、各ICには2つのトランジスタが含まれているため、各ウェーハ上に2 x 400 = 800のトランジスタが構築されます。各バッチで10枚のウェーハを処理すると、8000個のトランジスタを同時に製造できます。 ICで観察したさまざまなコンポーネントは何ですか?