多くの低コストインバータに共通する問題は、負荷条件に対して出力電圧を調整できないことです。このようなインバータでは、出力電圧は負荷が低くなると増加する傾向があり、負荷が高くなると低下します。

ここで説明する回路のアイデアは、さまざまな負荷に応じてさまざまな出力電圧条件を補償および調整するために、通常のインバータに追加できます。

デザイン#1:PWMを使用した自動RMS補正

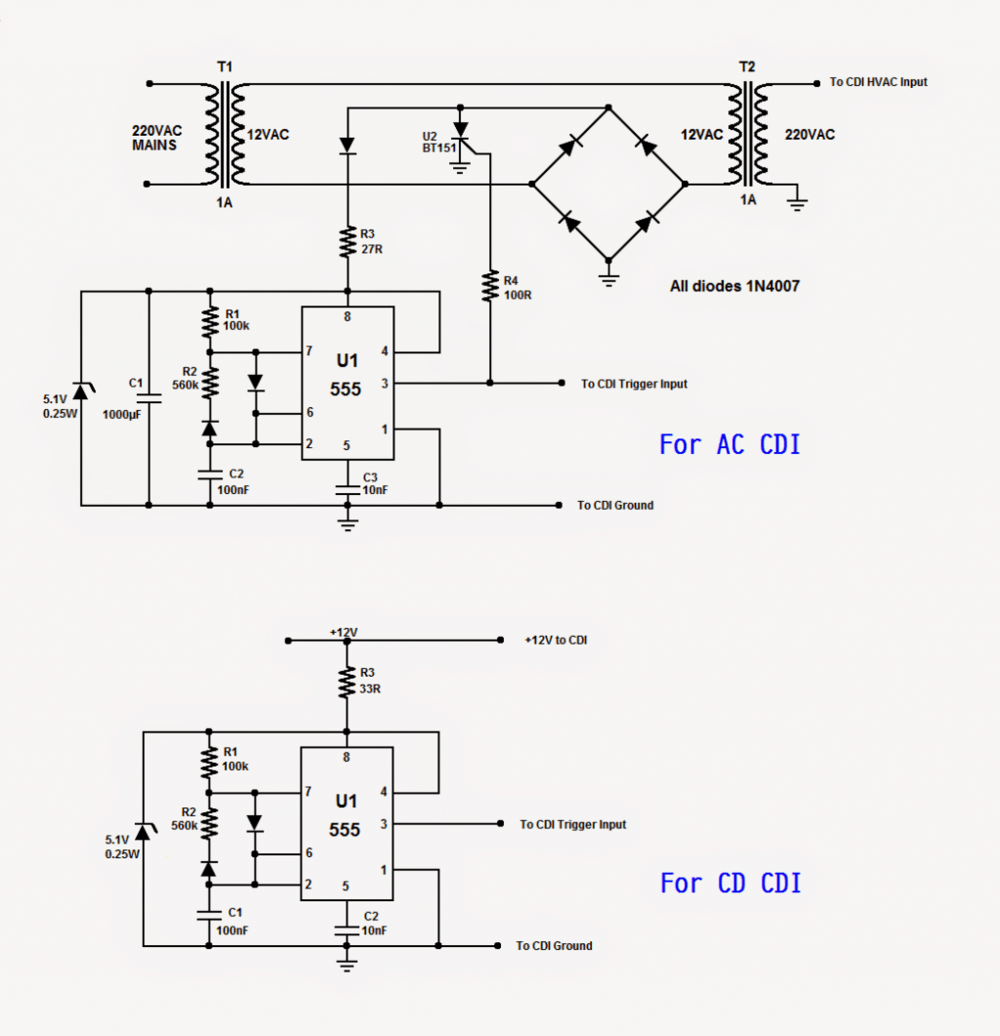

以下の最初の回路は、IC555からのPWMを使用して負荷に依存しない自動出力補正を実装する理想的なアプローチと見なすことができます。

上記の回路は、自動負荷トリガーRMSコンバーターとして効果的に使用でき、意図した目的のために通常のインバーターに適用できます。

IC 741は、電圧フォロワのように機能し、インバータ出力フィードバック電圧とPWMコントローラ回路の間のバッファのように機能します。

IC 741のピン#3に接続されている抵抗は 分圧器のように構成 、これは、主電源からの高AC出力を、インバーターの出力状態に応じて6〜12Vの間で変化する比例して低い電位に適切にスケールダウンします。

二つ IC555回路が構成されています 変調されたPWMコントローラーのように機能します。変調された入力はIC2のピン#5に適用され、ピン#6で信号を三角波と比較します。

これにより、ピン#3でPWM出力が生成され、ICのピン#5での変調信号に応答してデューティサイクルが変化します。

このピン#5で電位が上昇すると、世代全体のPWMまたはより高いデューティサイクルのPWMが発生し、その逆も同様です。

これは、オペアンプが 741が応答します インバータからの出力の上昇により電位が上昇すると、IC2 555の出力はPWMパルスを広げますが、インバータの出力が低下すると、PWMはIC2のピン#3で比例して狭くなります。

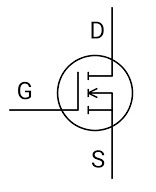

MOSFETを使用したPWMの構成。

上記の自動補正PWMが任意のインバーターのMOSFETゲートと統合されている場合、インバーターは負荷条件に応じてRMS値を自動的に制御できます。

負荷がPWMを超えると、インバーター出力が低くなる傾向があり、PWMが広がり、MOSFETがより強くオンになり、より多くの電流でトランスを駆動し、負荷から引き出される過剰な電流を補償します。

デザイン#2:オペアンプとトランジスタの使用

次のアイデアでは、負荷やバッテリ電圧の変化に応じて自動出力電圧調整を実現するために、通常のインバータを追加できるオペアンプバージョンについて説明します。

考え方は単純で、出力電圧が所定の危険しきい値を超えるとすぐに、対応する回路がトリガーされ、インバーターパワーデバイスが一貫した方法でオフになり、その結果、特定のしきい値内で出力電圧が制御されます。

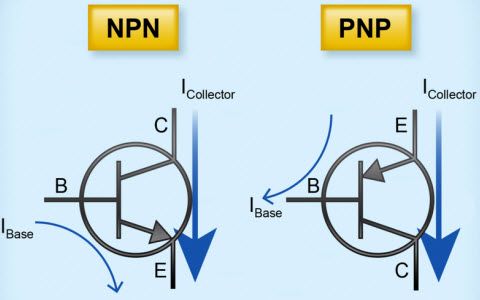

トランジスタを使用することの背後にある欠点は、関連するヒステリシスの問題である可能性があり、これにより、スイッチングがより広い断面にわたってかなり行われ、その結果、電圧レギュレーションがそれほど正確ではなくなる可能性があります。

一方、オペアンプは、非常に狭いマージン内で出力レギュレーションを切り替え、補正レベルを厳密かつ正確に保つため、非常に正確である可能性があります。

以下に示す単純なインバータ自動負荷電圧補正回路は、提案されたアプリケーションに、およびインバータの出力を任意の所望の制限内に調整するために効果的に使用することができる。

提案されたインバータ電圧補正回路は、以下の点の助けを借りて理解することができます。

単一のオペアンプがコンパレータと電圧レベル検出器の機能を実行します。

回路動作

変圧器出力からの高電圧ACは、分圧器ネットワークを使用して約14Vに降圧されます。

この電圧は、動作電圧と回路の検出電圧になります。

分圧器を使用した降圧電圧は、出力の電圧の変化に比例して対応します。

オペアンプのピン3は、制御が必要な制限に対応する等価DC電圧に設定されています。

これは、回路に必要な最大制限電圧を供給し、出力がちょうどハイになってNPNトランジスタをトリガーするまで10kプリセットを調整することによって行われます。

上記の設定が完了すると、回路は意図された修正のためにインバーターと統合される準備が整います。

ご覧のとおり、NPNのコレクターは、インバーター変圧器への電力供給を担当するインバーターのMOSFETのゲートに接続する必要があります。

この統合により、出力電圧が設定された制限を超える傾向がある場合は常に、NPNトリガーがMOSFETのゲートを接地し、それによって電圧のそれ以上の上昇を制限し、出力電圧が周囲に浮かんでいる限り、ON / OFFトリガーが無限に継続します。危険区域。

NPN統合はNチャネルMOSFETとのみ互換性があることに注意する必要があります。インバータがPチャネルMOSFETを搭載している場合、回路構成ではトランジスタとオペアンプの入力ピン配列を完全に反転させる必要があります。

また、回路のアースは、インバーターのバッテリーのマイナスと共通にする必要があります。

デザイン#3:はじめに

この回路は、私の友人の1人であるSam氏から要求されました。彼の絶え間ないリマインダーにより、インバーターアプリケーションにこの非常に便利なコンセプトを設計するように促されました。

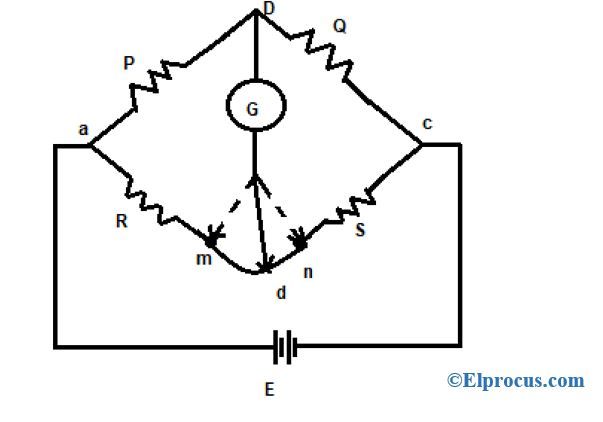

“自動電圧調整器の動作原理 ”

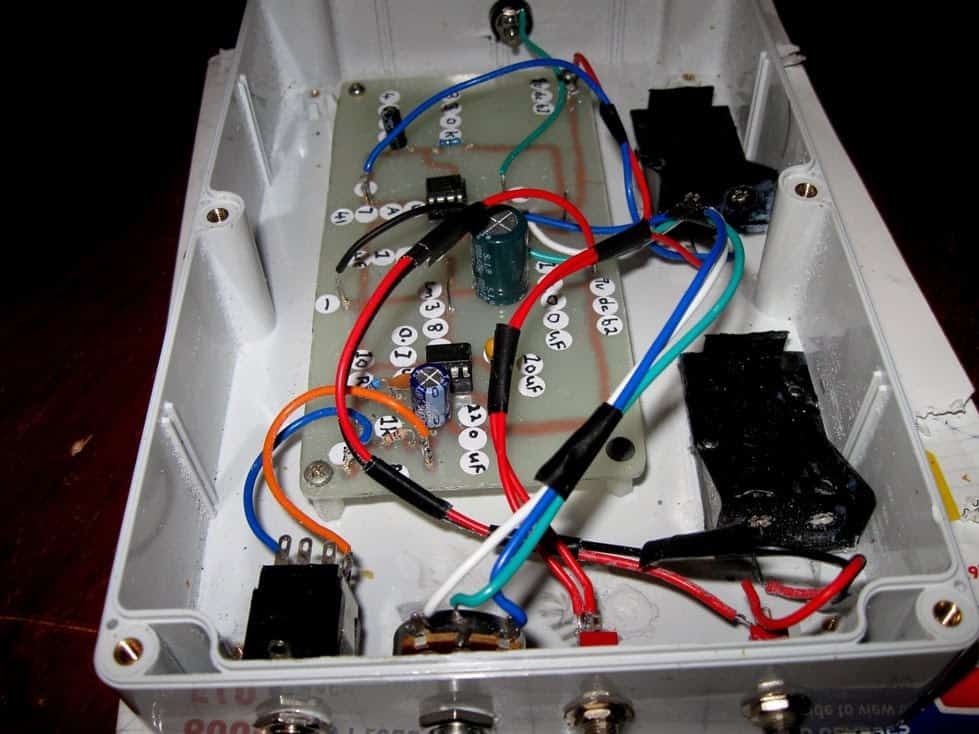

ここで説明する負荷独立/出力補正または出力補償インバータ回路は、概念レベルのみであり、私は実際にテストしていませんが、そのシンプルな設計のため、アイデアは実現可能に見えます。

回路動作

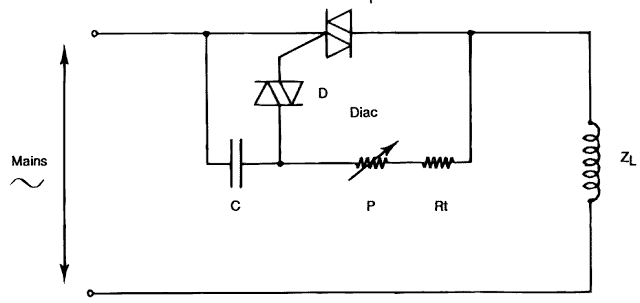

この図を見ると、全体の設計は基本的にIC555を中心に構築された単純なPWMジェネレータ回路であることがわかります。

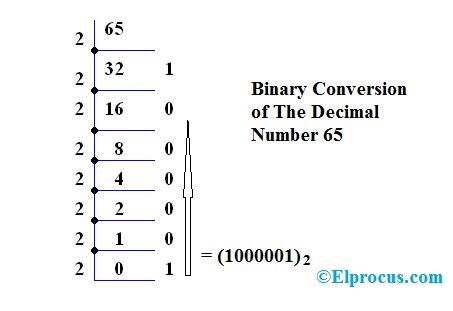

この標準の555PWM設計では、R1 / R2の比率を変更することでPWMパルスを最適化できることがわかっています。

この事実は、ここではインバータの負荷電圧補正アプリケーションに適切に利用されています。

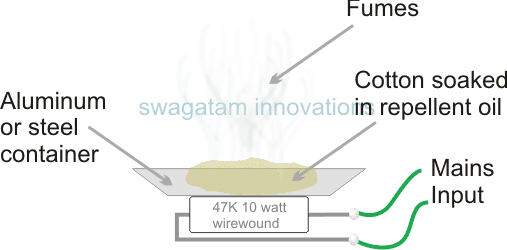

アン LED / LDRをシールして作られたオプトカプラー オプトのLDRが回路のPWM「アーム」の抵抗の1つになる配置が使用されています。

オプトカプラーのLEDは、インバーター出力または負荷接続からの電圧によって点灯します。

主電源電圧は、オプトLEDに給電するためのC3および関連コンポーネントを使用して適切に降下されます。

回路をインバーターに統合した後、システムに電力が供給されると(適切な負荷が接続されている場合)、出力でRMS値が測定され、出力電圧が負荷にちょうど適したものになるようにプリセットP1が調整されます。

設定方法

この設定がおそらく必要なすべてです。

ここで、負荷が増加すると、電圧が出力で低下する傾向があり、その結果、オプトLEDの強度が低下するとします。

LEDの強度が低下すると、ICはPWMパルスを最適化して、出力電圧のRMSが上昇し、電圧レベルも必要なマークまで上昇します。この開始は、LEDの強度にも影響します。これで明るくなり、最終的に自動的に最適化されたレベルに到達し、出力でのシステム負荷電圧条件のバランスを正しく取ります。

ここで、マーク比は主に必要なパラメータを制御することを目的としているため、オプトは示されているものの左腕または右腕のいずれかに適切に配置する必要があります PWM制御 ICのセクション。

この500ワットのインバーター回路に示されているインバーター設計で回路を試すことができます

パーツリスト

- R1 = 330K

- R2 = 100K

- R3、R4 = 100オーム

- D1、D2 = 1N4148、

- D3、D4 = 1N4007、

- P1 = 22K

- C1、C2 = 0.01uF

- C3 = 0.33uF / 400V

- OptoCoupler =自家製、LED / LDRを遮光容器内で向かい合わせに密封します。

注意:提案された設計は、インバーターの主電源電圧から分離されていません。テストおよびセットアップ手順中は、細心の注意を払ってください。

前:このサーモタッチ操作スイッチ回路を作成する 次へ:このEMFポンプ回路を作り、ゴーストハンティングに行く