この投稿では、ディスクリート トランジスタを使用して、NOT、AND、NAND、OR、および NOR 論理ゲートを構築する方法を学習します。トランジスタ論理ゲートを使用する主な利点は、1.5 V という低い電圧でも動作できることです。

一部の電子アプリケーションでは、使用可能な電圧が TTL や CMOS IC に電力を供給するには不十分な場合があります。これは、バッテリーで動作するガジェットに特に当てはまります。間違いなく、常に 3 ボルト ロジック IC のオプションがあります。ただし、これらは愛好家や実験者にとって常に簡単にアクセスできるとは限らず、定義された電圧仕様 (通常は DC 2.5 ボルト未満) では動作しません。

さらに、バッテリ駆動のアプリケーションでは、1.5 ボルトのバッテリを 1 つしか使用できない場合があります。さて、あなたは何をするつもりですか?いつもの IC論理ゲート トランジスタ化された論理ゲートに置き換えることができます。特定の論理ゲートごとに、通常は数個のトランジスタが必要であり、典型的な NOT ゲート インバータ ロジックの場合、必要なトランジスタは 1 つだけです。

FET とバイポーラ トランジスタ

電界効果トランジスタ (FET) vs バイポーラトランジスタ : 低電圧ロジック回路に適したオプションはどれですか?の大きな特徴の一つ 事実 「オン」抵抗が信じられないほど低いということです。さらに、非常に低いゲートターンオン電流が必要です。

ただし、非常に低電圧のアプリケーションでは、1 つの制限があります。通常、ゲート電圧の制限は 1 ボルト程度です。さらに、電流制限抵抗またはプルダウン抵抗がゲートに接続されている場合、使用可能な電圧が FET の最適動作範囲を下回る可能性があります。

逆に、バイポーラ スイッチング トランジスタは、オンにするのに 0.6 ~ 0.7 ボルトしか必要としないため、非常に低電圧の単一バッテリ アプリケーションに有利です。

さらに、最寄りの電器店でバブルパックで通常販売されている一般的な FET の大部分は、多くの場合、バイポーラ トランジスタよりも高価です。また、バイポーラ トランジスタのバルク パケットは、通常、一対の FET の価格で購入できます。

FET の取り扱いには、バイポーラ トランジスタの取り扱いよりもはるかに注意が必要です。静電および一般的な実験的誤用により、FET は特に損傷を受けやすくなります。焦げたコンポーネントは、デバッグの感情的な苦痛を忘れないように、実験や革新の楽しい創造的な夜を台無しにする可能性があります.

スイッチングトランジスタの基礎

この記事で説明する論理回路の例では、バイポーラ NPN トランジスタを使用しています。これは、手頃な価格であり、特別な処理を必要としないためです。デバイスまたはそれをサポートする部品の損傷を避けるために、回路を接続する前に適切な安全対策を講じる必要があります。

私たちの回路は主にバイポーラ ジャンクション トランジスタ (BJT) に集中していますが、FET テクノロジを使用して同様にうまく構築できた可能性があります。

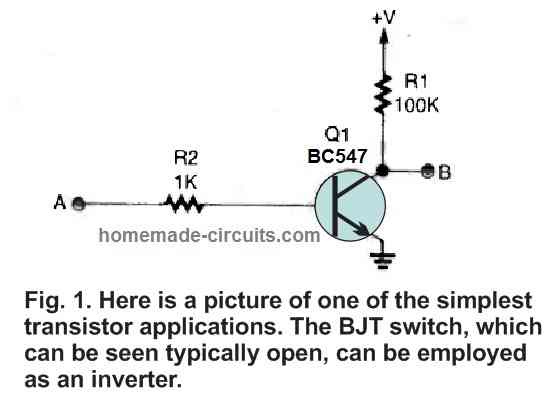

基本的なスイッチ回路は単純なトランジスタ アプリケーションであり、最も簡単な設計の 1 つです。

単一のトランジスタで NOT ゲートを作成する

トランジスタ スイッチの回路図を図 1 に示します。特定のアプリケーションでの実装方法に応じて、スイッチはローに維持されるか、通常は開いているように見えます。

単純な NOT ゲート インバーター ロジック ゲートは、図 1 に示す簡単なスイッチング回路によって作成できます (ポイント A は入力です)。 NOT ゲートは、DC バイアスがトランジスタのベース (ポイント A; Q1) に供給されない場合、遮断されたままになり、出力でハイまたはロジック 1 (V+ レベルに等しい) になるように動作します (ポイントB)。

ただし、適切なバイアスが Q1 のベースに供給されると、トランジスタがアクティブになり、回路の出力がローまたはロジック 0 (ゼロ電位にほぼ等しい) になります。 Q1 と指定されたトランジスタは、汎用バイポーラ トランジスタ、または BC547 であり、通常、低電力スイッチングおよびアンプ アプリケーションで使用されます。

それと同等のトランジスタ(2N2222、2N4401など)はすべて機能します。 R1 と R2 の値は、低電流ドレインと互換性の間で妥協するように選択されました。すべての設計で、抵抗器はすべて 1/4 ワット、5% 単位です。

供給電圧は、1.4 ~ 6 ボルト DC の間で調整可能です。負荷抵抗と出力接続がトランジスタのエミッタにシフトされると、回路はバッファのように機能することに注意してください。

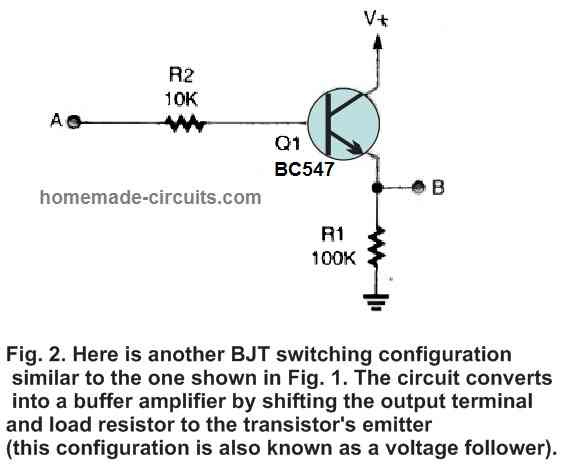

単一の BC547 BJT を使用してバッファー ゲートを作成する

電圧フォロワ、またはバッファ アンプは、図 2 に示すものと同じロジック スイッチング構成の一種です。この回路では、負荷抵抗と出力端子がトランジスタのコレクタからエミッタにシフトされていることに注意してください。この設計と図 1 に示す設計との主な違い。

トランジスタの機能は、負荷抵抗と出力端子を BJT のもう一方の端に移動することによって「反転」することもできます。

言い換えると、回路の入力にバイアスが供給されていない場合、回路の出力はローのままです。ただし、適切な電圧のバイアスが回路の入力に供給されると、回路の出力は高くなります。 (これは、以前の回路で起こったこととは正反対です。)

トランジスタを使用した 2 入力論理ゲートの設計

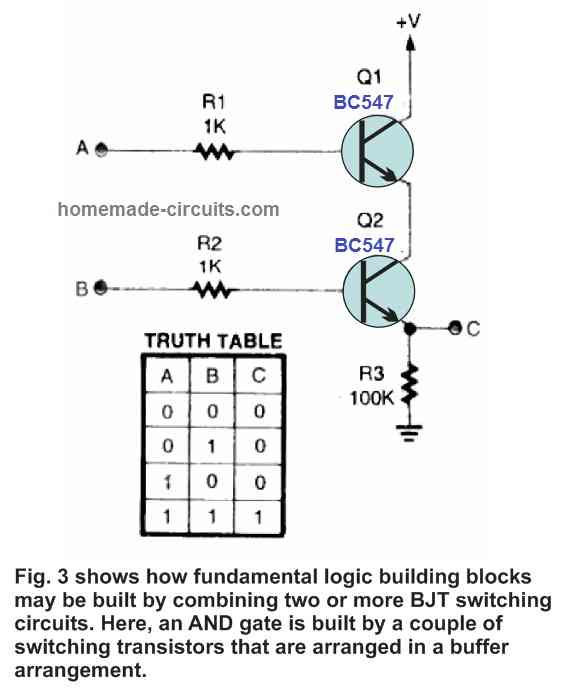

2つのトランジスタを使用したANDゲート

図 3 は、1 組のバッファーを使用して基本的な 2 入力 AND ゲートを作成する方法と、そのゲートの真理値表を示しています。真理値表は、個別の入力セットごとに出力結果がどうなるかを示しています。ポイント A と B は回路の入力として使用され、ポイント C は回路の出力として機能します。

真理値表から、入力パラメータの 1 つのセットのみが論理ハイの出力信号になるのに対して、他のすべての入力の組み合わせは論理ローの出力になることに注意することが重要です。図 3 の AND ゲートの出力は、いったんハイになると、V+ よりわずかに低いままです。

これは、2 つのトランジスタ (Q1 と Q2) 間の電圧降下が原因で発生します。

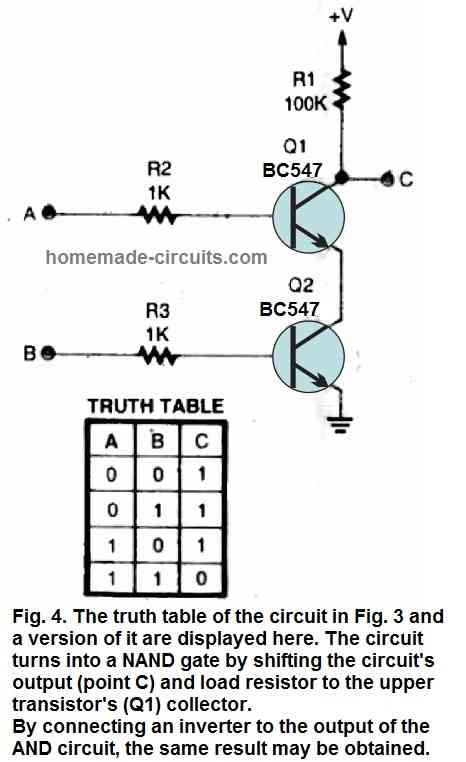

2つのトランジスタを使用したNANDゲート

図 3 の回路の別の変形と、関連する真理値表を図 4 に示します。この回路は、出力 (ポイント C) と出力抵抗を上部トランジスタ (Q1) のコレクタにシフトすることにより、NAND ゲートになります。

R1 のローサイドをグランドに引き下げるには、Q1 と Q2 の両方をオンにする必要があるため、出力 C での電圧損失はわずかです。

トランジスタANDまたはトランジスタNANDゲートが3つ以上の入力を必要とする場合、3つ、4つなどの入力ANDまたはNANDゲートを提供するために、より多くのトランジスタを図示の設計に接続することができる。

ただし、個々のトランジスタの電圧損失を補償するために、V+ をそれに応じて増加させる必要があります。

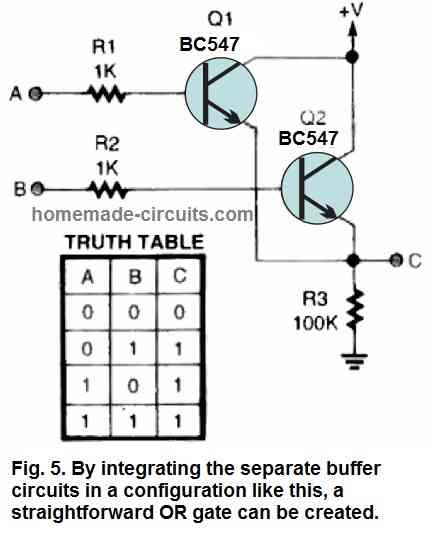

2 つのトランジスタを使用した OR ゲート

図 5 には、OR ゲート回路の真理値表と共に、2 つの入力を持つ別の形式の論理回路が示されています。

入力Aまたは入力Bのいずれかがハイにプッシュされると、回路の出力はハイになりますが、カスケード接続されたトランジスタにより、電圧降下は0.5ボルトを超えます。繰り返しになりますが、表示された数値は、後続のトランジスタゲートを動作させるのに十分な電圧と電流があることを示しています。

2 つのトランジスタを使用した NOR ゲート

図 6 は、リストの次のゲートである 2 入力 NOR ゲートと、その真理値表を示しています。 AND ゲートと NAND ゲートが互いに応答する方法と同様に、OR 回路と NOR 回路も同じように動作します。

表示されている各ゲートは、少なくとも 1 つまたは複数の隣接するトランジスタ ゲートをアクティブにするのに十分なドライブを供給することができます。

トランジスタ ロジック ゲート アプリケーション

あなたが今持っている上記のデジタル回路で何をしますか?従来の TTL または CMOS ゲートで達成できることは何でも、電源電圧の制限を心配する必要はありません。ここでは、動作中のトランジスタ ロジック ゲートのいくつかのアプリケーションを示します。

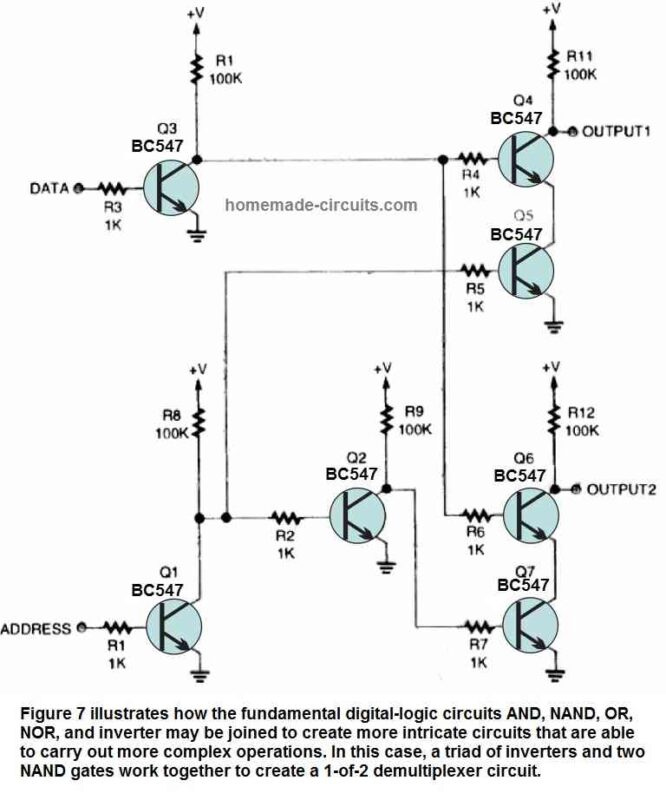

デマルチプレクサ回路

3 つの NOT ゲートと 2 つの NAND 回路を備えた 1-of-2 デマルチプレクサを図 7 に示します。適切な出力は、駆動情報が適用されている間に、OUTPUT1 または OUTPUT2 のいずれかである 1 ビットの「アドレス入力」を使用して選択されます。 DATA 入力を使用して回路に接続します。

この回路は、データ レートが 10 kHz 未満に維持されている場合に最も効果的に動作します。回路の機能は簡単です。 DATA 入力には必要な信号が供給され、Q3 がオンになり、Q3 のコレクタで入力データが反転されます。

ADDRESS 入力がローの場合 (接地されているか、信号が提供されていない場合)、Q1 の出力はハイに駆動されます。 Q1 のコレクタでは、高出力が 2 つのパスに分割されます。最初のパスでは、Q1 の出力が Q5 のベース (2 入力 NAND ゲートのレッグの 1 つ) に供給され、Q5 をオンにして、Q4 と Q5 で構成される NAND ゲートを「アクティブ化」します。

2 番目のパスでは、Q1 の高出力が同時に別の NOT ゲート (Q2) の入力に供給されます。二重反転の後、Q2 の出力はローになります。このローは、Q7 のベース (Q6 と Q7 で構成される第 2 の NAND ゲートの 1 つの端子) に供給され、NAND 回路をオフに切り替えます。

このような状況では、DATA 入力に適用された情報または信号はすべて OUTPUT1 に到達します。あるいは、ハイ信号が ADDRESS 入力に与えられると、状況は逆になります。つまり、Q4/Q5 NAND ゲートが無効になり、Q6/Q7 NAND ゲートが有効になるため、回路に提供される情報はすべて OUTPUT2 に表示されます。

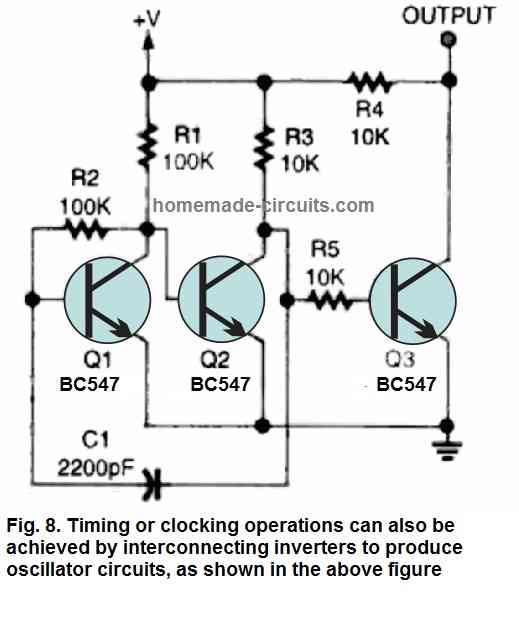

発振回路(クロックジェネレータ)

図 8 に示す次のトランジスタ論理ゲート アプリケーションは、3 つの通常の NOT ゲート インバータ (そのうちの 1 つがフィードバック抵抗 R2 を使用してバイアスされ、それをアナログ領域)。

出力を四角形にするために、オシレータ出力の補数を供給する 3 番目の NOT ゲート (Q3) が含まれています。 C1 値を増減して、回路の動作周波数を変更できます。出力波形の周波数は約 7 kHz で、V+ は DC 1.5 ボルトで、示されたコンポーネント値を使用します。

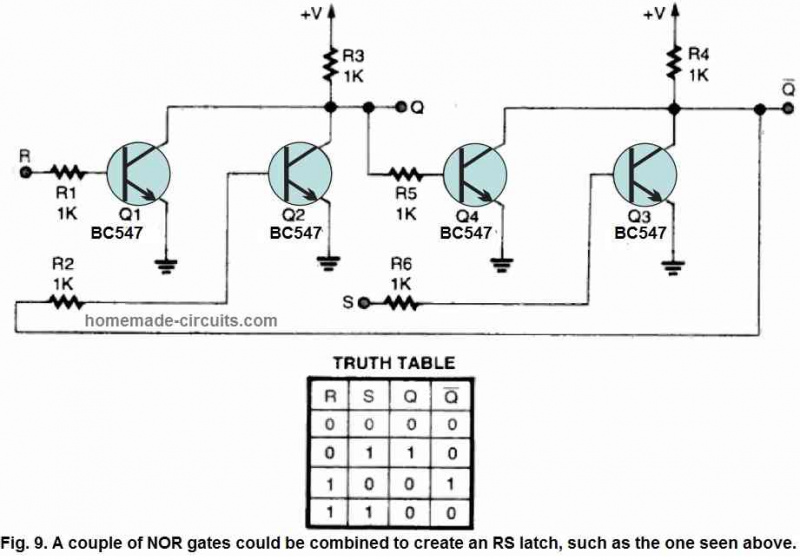

RS ラッチ回路

図 9 は、2 つの NOR ゲートで構成される RS ラッチの最終的なアプリケーション回路を示しています。 Q および Q 出力で健全な出力ドライブを確保するために、抵抗 R3 および R4 を 1k オームに調整します。

RS ラッチの真理値表は、回路図デザインと一緒に表示されます。これらは、個々のトランジスタを使用して作成できる、信頼できる低電圧のデジタル論理ゲート回路のほんの一部です。

トランジスタ化されたロジックを使用する回路には部品が多すぎる

これらの低電圧トランジスタ化ロジック回路をすべて使用することで、多くの問題を解決できます。ただし、これらのトランジスタ化されたゲートを多用すると、新たな問題が発生する可能性があります。

構築しているアプリケーションに大量のゲートが含まれており、貴重なスペースを占有している場合、トランジスタ化と抵抗の数はかなり膨大になる可能性があります。

この問題を解決する方法の 1 つは、個々のユニットの代わりにトランジスタ アレイ (プラスチックで囲まれた多数のトランジスタ) と SIP (Single Inline Package) 抵抗を使用することです。

上記のアプローチは、フルサイズの同等品と同等のパフォーマンスを維持しながら、PCB 上のスペースを大幅に節約できます。トランジスタ アレイは、表面実装、14 ピン スルーホール、およびクワッド パック パッケージで提供されます。

ほとんどの回路では、トランジスタの種類を混在させても問題ありません。

それにもかかわらず、実験者は、トランジスタ化された論理回路を構築するために単一のタイプのトランジスタで作業することをお勧めします (つまり、BC547 を使用してゲートのセクションを作成する場合は、残りのゲートを作成するために同じ BJT を使用してみてください)。

その理由は、さまざまなトランジスタのバリエーションが多少異なる特性を持つ可能性があり、したがって異なる動作をする可能性があるためです。

たとえば、一部のトランジスタでは、ベース スイッチ ON 制限が別のトランジスタよりも大きいか小さいか、全体的な電流ゲインが少し高いか低い場合があります。

一方、単一タイプのトランジスタのバルクボックスを購入するコストも低くなる可能性があります。論理ゲートが整合トランジスタを使用して構築されている場合、回路のパフォーマンスが向上し、プロジェクト全体が最終的によりやりがいのあるものになります.