MOS トランジスタは、大規模集積回路設計における最も基本的な要素です。これらのトランジスタは、大まかにPMOSとNMOSの2種類に分類される。 NMOS トランジスタと PMOS トランジスタの組み合わせは、 CMOSトランジスタ .異なる 論理ゲート & 実装されるその他のデジタル ロジック デバイスには、PMOS ロジックが必要です。この技術は安価であり、干渉に対して優れた耐性があります。この記事では、PMOS トランジスタのような MOS トランジスタのタイプの 1 つについて説明します。

PMOSトランジスタとは?

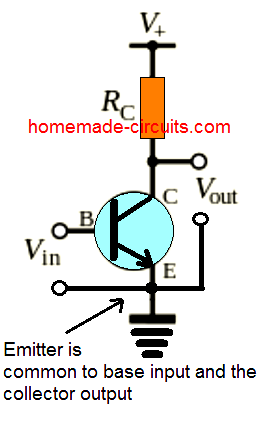

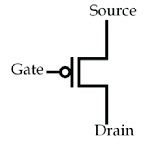

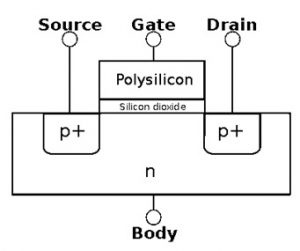

PMOSトランジスタまたはPチャネル金属酸化物半導体は、p型ドーパントがチャネルまたはゲート領域で利用される一種のトランジスタである。このトランジスタは、NMOS トランジスタの正反対です。これらのトランジスタには 3 つの主端子があります。トランジスタのソースがp型基板で設計され、ドレイン端子がn型基板で設計されているソース、ゲート、ドレイン。このトランジスタでは、正孔のような電荷キャリアが電流の伝導に関与しています。 PMOS トランジスタの記号を以下に示します。

PMOSトランジスタはどのように機能しますか?

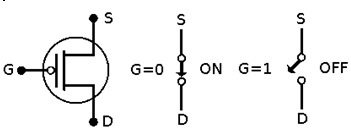

p型トランジスタの動作は、n型トランジスタとは正反対です。このトランジスタは、無視できない電圧になると開回路を形成します。つまり、ゲート(G)端子からソース(S)への電気の流れはありません。同様に、このトランジスタは、電圧が約0ボルトになると閉回路を形成します。これは、電流がゲート(G)端子からドレイン(D)に流れることを意味します。

このバブルは反転バブルとも呼ばれます。したがって、この円の主な機能は、入力電圧値を反転することです。ゲート端子が1の電圧を提供する場合、このインバーターはそれをゼロに変更し、それに応じて回路を機能させます。したがって、PMOSトランジスタとNMOSトランジスタの機能はまったく逆です。それらを1つのMOS回路に融合すると、CMOS(相補型金属酸化膜半導体)回路になります。

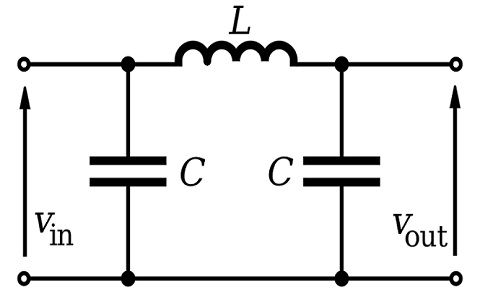

PMOSトランジスタの断面図

PMOSトランジスタの断面図を以下に示します。 pMOS トランジスタは、ゲートに隣接する 2 つの p 型半導体領域を含む n 型ボディで構築されます。このトランジスタには、図に示すように、ソースとドレインのような2つの端子間の電子の流れを制御する制御ゲートがあります。 pMOS トランジスタでは、ボディは +ve 電圧に保持されます。ゲート端子が正になると、ソース端子とドレイン端子が逆バイアスされます。これが起こると、電流が流れなくなるので、トランジスタはオフになります。

ゲート端子の電圧供給が低下すると、正の電荷キャリアが Si-SiO2 界面の底に引き寄せられます。電圧が十分に低くなると、チャネルが反転し、電流の流れを可能にすることでソース端子からドレインへの導電経路が作成されます。

これらのトランジスタがデジタルロジックを扱うときはいつでも、通常、1と0(ONとOFF)のような2つの異なる値があります。トランジスタの正の電圧は VDD として知られており、デジタル回路内の論理ハイ (1) 値を表します。の VDD 電圧レベル TTL ロジック 大体5V前後でした。現在、トランジスタは通常 1.5V ~ 3.3V の範囲であるため、実際にはこのような高電圧に耐えることができません。低電圧は、多くの場合、GND または VSS として知られています。したがって、VSS は論理「0」を意味し、通常は 0V に設定されます。

PMOSトランジスタ回路

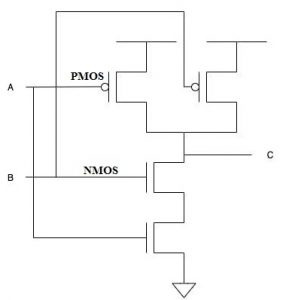

PMOSトランジスタとNMOSトランジスタを使用したNANDゲートの設計を以下に示します。一般に、デジタル エレクトロニクスにおける NAND ゲートは、NOT-AND ゲートとも呼ばれる論理ゲートです。このゲートの出力は、2 つの入力がハイ (1) で、その出力が AND ゲートの補数である場合にのみロー (0) になります。 2 つの入力のいずれかが LOW (0) の場合、高い出力結果が得られます。

以下の論理回路では、入力 A が 0 で B が 0 の場合、pMOS の A 入力は「1」を生成し、nMOS の A 入力は「0」を生成します。したがって、この論理ゲートは、閉回路によってソースに接続され、開回路によって GND から切り離されているため、論理「1」を生成します。

A が「0」で B が「1」の場合、pMOS の A 入力は「1」を生成し、NMOS の A 入力は「0」を生成します。したがって、このゲートは閉回路を介してソースに接続され、開回路によってGNDから切り離されているため、論理1を生成します。 A が「1」で B が「0」の場合、pMOS の「B」入力は高出力 (1) を生成し、NMOS の「B」入力は出力を低 (0) として生成します。したがって、この論理ゲートは、閉回路を介してソースに接続され、開回路によってGNDから切り離されているため、論理1を生成します。

Aが「1」でBが「1」の場合、pMOSのA入力はゼロを生成し、nMOSのA入力は「1」を生成します。したがって、pMOS と nMOS の B 入力も検証する必要があります。 pMOS の B 入力は「0」を生成し、nMOS の B 入力は「1」を生成します。したがって、この論理ゲートは、開回路によってソースから切り離され、閉回路を介して GND に接続されるため、論理「0」を生成します。

真理値表

上記の論理回路の真理値表を以下に示します。

|

あ |

B |

C |

|

0

|

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

PMOS トランジスタのしきい値電圧は通常、チャネル反転として知られるチャネルを作成するために必要な「Vgs」です。 PMOSトランジスタでは、基板とソース端子は単に「Vdd」に接続されています。ゲート端子のソース端子を基準にして Vdd からチャネル反転に気付くポイントまで電圧を下げ始めると、この位置で Vgs とソースが高電位にあることを分析すると、負の値が得られます。したがって、PMOS トランジスタの Vth 値は負になります。

PMOS 製造プロセス

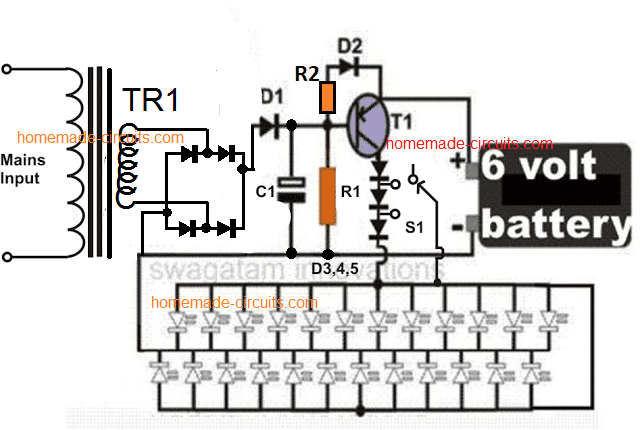

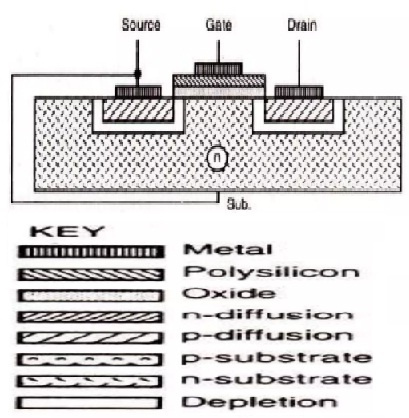

PMOSトランジスタの製造に含まれるステップを以下に説明する。

ステップ1:

リン材料をドーピングするだけで、薄いシリコンウェーハ層がN型材料に変わります。

ステップ2:

厚い二酸化シリコン (Sio2) 層が完全な p 型基板上に成長します。

ステップ3:

ここで、厚い二酸化シリコン層の上にフォトレジストで表面をコーティングします。

ステップ4:

その後、この層は、トランジスタチャネルとともに拡散が行われる領域を定義するマスクを通してUV光に単純にさらされます。

ステップ5:

これらの領域は、下にある二酸化シリコンと相互にエッチング除去されるため、マスクによって画定されたウィンドウ内でウェーハの表面が露出されます。

ステップ6:

残りのフォトレジストが取り除かれ、薄い SiO2 層がチップの表面全体に通常 0.1 マイクロメートル成長します。その後、その上にポリシリコンを載せてゲートの構造を形成します。フォトレジストをポリシリコン層全体に配置し、マスクを通して UV 光を照射します2。

ステップ 7:

拡散は、ウェーハを最高温度まで加熱し、ホウ素などの目的の p 型不純物を含むガスを通過させることによって達成されます。

ステップ8:

厚さ1マイクロメートルの二酸化シリコンを成長させ、その上にフォトレジスト材料を堆積させます。コンタクトカットを行うためにエッチングされたゲート、ソース、ドレインの優先領域に mask3 を使用して紫外光を照射します。

ステップ9:

ここで、金属またはアルミニウムが 1 マイクロメートルの厚さの表面に堆積されます。ここでも、フォトレジスト材料が金属全体に成長し、必要な相互接続設計を形成するためにエッチングされたマスク 4 を通して UV 光を照射します。最終的な PMOS 構造を以下に示します。

PMOSトランジスタの特性

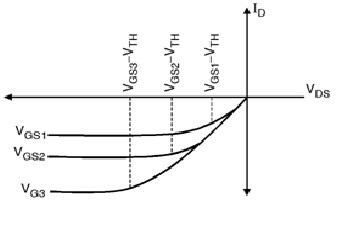

PMOS トランジスタの I-V 特性を以下に示します。これらの特性は、ドレインからソースへの電流 (I DS) と、線形および飽和領域のようなその端子電圧との間の関係を取得するために、2 つの領域に分割されます。

線形領域では、VDS (ドレインからソースへの電圧) が増加すると IDS は直線的に増加しますが、飽和領域では IDS は安定しており、VDS に依存しません。 ISD (ソースからドレインへの電流) とその端子電圧の間の主な関係は、NMOS トランジスタと同様の手順で導き出されます。この場合、唯一の変化は、反転層内に存在する電荷キャリアが単なる正孔であることです。正孔がソースからドレインに移動するとき、電流の流れも同じです。

したがって、負の符号が現在の方程式内に表示されます。さらに、デバイスの端子に印加されるすべてのバイアスは負です。そこで、PMOSトランジスタのID-VDS特性を以下に示します。

線形領域での PMOS トランジスタのドレイン電流の式は、次のように与えられます。

ID = – mp コックス

同様に、飽和領域での PMOS トランジスタのドレイン電流の式は次のように与えられます。

ID = – mp Cox (VSG – | V TH |p )^2

ここで、「mp」は穴の可動性と「|VTH|」です。 p' は PMOS トランジスタのしきい値電圧です。

上記の式で、負の符号は ID( ドレイン電流 ) はドレイン (D) からソース (S) に流れますが、正孔は反対方向に流れます。正孔の移動度が電子の移動度に比べて低い場合、PMOS トランジスタは低電流駆動能力に悩まされます。

したがって、これはすべて PMOS トランジスタまたは p 型 mos トランジスタの概要 (製造、回路、およびその動作) に関するものです。 PMOS トランジスタが設計されています p-ソース、n-基板、およびドレインを備えています。 PMOSの電荷キャリアは正孔です。このトランジスタは、ゲート端子に低電圧が印加されると導通します。 PMOS ベースのデバイスは、NMOS デバイスに比べて干渉を受けにくいです。これらのトランジスタは、電圧制御抵抗器、アクティブ負荷、電流ミラー、トランスインピーダンス アンプとして使用でき、スイッチや電圧アンプにも使用できます。ここで質問です。NMOS トランジスタとは何ですか?