JTAG(Joint Test Action Group)は、電子ボード内で発生した製造上の問題を解決するために1980年に開発された確立されたIEEE1149.1標準です。 プリント回路基板 。このテクノロジーは、テストアクセスが減少しているときに、各複雑なボードに十分なテストアクセスを提供するために使用されます。このようにして、バウンダリスキャン技術が発表され、JTAG標準または JTAG仕様 確立されています。電子機器の複雑さは日々高まっているため、JTAG仕様は、複雑でコンパクトな電子機器ユニットをテストするための受け入れられたテスト形式になっています。この記事では、 JTAG プロトコル–アプリケーションの操作。

JTAGとは何ですか?

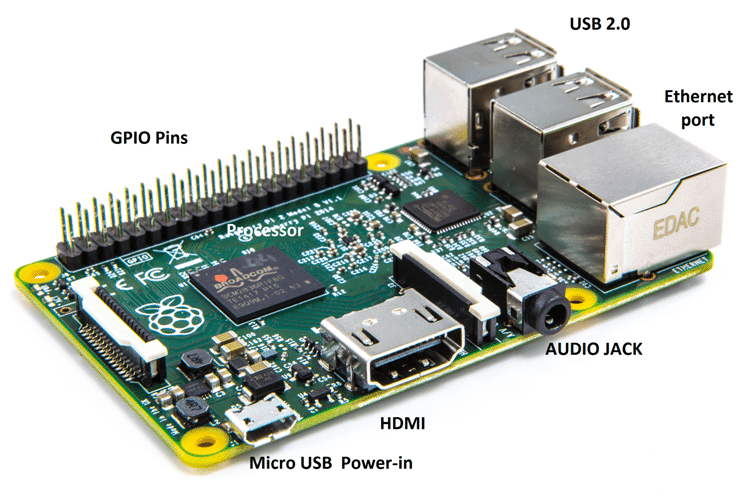

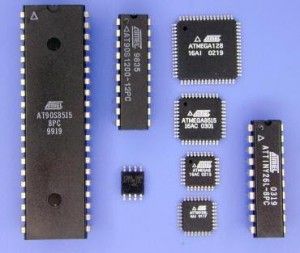

IEEE 1149.1標準テストアクセスポートおよびバウンダリスキャンアーキテクチャに付けられた名前は、JTAG(Joint Test Action Group)として知られています。このバウンダリスキャンアーキテクチャは、主にコンピュータ内で使用されます プロセッサー JTAGを搭載した最初のプロセッサがIntelによってリリースされたためです。このIEEE規格は、製造手順の後でコンピュータが正しく機能しているかどうかを確認するために、コンピュータの回路をテストする方法を定義しているだけです。回路基板上で、はんだ接合をチェックするためのテストが実行されます。

共同テストアクショングループは、回路基板内の障害を特定するのに役立つすべてのICパッドを備えたテスターのピン配置ビューを提供します。このプロトコルがチップに接続されると、開発者がチップと他のチップとの接続を制御できるようにすることで、プローブをチップに接続できます。共同テストアクショングループとのインターフェイスは、ファームウェアを電子デバイスの不揮発性メモリにコピーするために開発者が使用することもできます。

“デジタル信号とは ”

構成/ピン配置

共同テストアクショングループには20ピンが含まれ、各ピンとその機能について以下で説明します。

ピン1(VTref): これは、1.5〜5.0VDCの範囲のターゲットの主電源に接続するために使用されるターゲット基準電圧ピンです。

ピン2(Vsupply): これは、ターゲット1.5VDC〜5.0VDCのメイン電圧供給を接続するために使用されるターゲット供給電圧です。

ピン3(nTRST): これは、TAPコントローラーのステートマシンをリセットするために使用されるテストリセットピンです。

ピン(4、6、8、10、12、14、16、18、20): これらは共通のGNDピンです。

ピン5(TDI): これはピンのテストデータです。このデータはターゲットデバイスにシフトされます。このピンは、ターゲットボード上で定義された条件でプルアップする必要があります。

Pin7(TMS): これは、TAPコントローラーのステートマシンの次の状態を判別するためにプルされるテストモードステートピンです。

ピン9(TCK): これは、TAPコントローラーの内部ステートマシンの動作を同期するテストクロックピンです。

ピン11(RTCK): これは、アダプティブクロッキングをサポートするデバイスで使用される入力リターンTCKピンです。

ピン13(TDO): これはテストデータ出力ピンであるため、データはターゲットデバイスからFlyswatterに移動されます。

ピン15(nSRST): これは、ターゲットのメインリセット信号に接続されているターゲットシステムリセットピンです。

ピン17および19(NC): これらは接続されたピンではありません。

JTAGワーキング

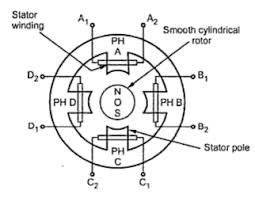

JTAGの本来の用途は、境界テストです。これは、CPUとのような2つのICを含む単純なプリント回路基板です。 FPGA 。一般的なボードには、多くのICが含まれている場合があります。一般に、ICには、多くの接続と一緒に接続された多くのピンが含まれています。ここで、次の図では、4つの接続のみが示されています。

したがって、すべてのボードに数千の接続がある多くのボードを設計する場合。その中に、いくつかの悪いボードがあります。したがって、どのボードが機能していて、どのボードが機能していないかを確認する必要があります。そのために、共同テストアクショングループが設計されました。

このプロトコルはすべてのチップの制御ピンを使用できますが、次の図では、Joint TestActionGroupがCPUのすべての出力ピンとFPGAのすべての入力ピンを作成します。その後、CPUのピンからある程度のデータを送信し、FPGAからピンの値を読み取ることにより、JTAGはPCBボードの接続に問題がないことを示します。

実際、Joint Test Action Groupには、TDI、TDO、TMS、およびTCKの4つの論理信号が含まれています。そして、これらの信号は特定の方法で接続する必要があります。最初に、TMSとTCKはJTAGのすべてのICに並列に接続されます。

その後、TDIとTDOの両方が接続されてチェーンが形成されます。ご覧のとおり、すべてのJTAG準拠ICには、3ピンが入力で4番目のピンが出力であるJTAGに使用される4ピンが含まれています。 TRSTのような5番目のピンはオプションです。通常、JTAGピンは他の目的で共有されません。

共同テストアクショングループを使用することにより、すべてのICは、元の理由がJTAGによって作成された境界テストを利用します。現在、このプロトコルの使用法は、FPGAの構成などのさまざまな機能を許可するように拡張されており、その後、デバッグ目的でJTAGがFPGAコアで使用されます。

JTAGアーキテクチャ

JTAGアーキテクチャを以下に示します。このアーキテクチャでは、デバイスのコアロジックとピンの間のすべての信号が、BSRまたはバウンダリスキャンレジスタと呼ばれるシリアルスキャンパスを介して中断されます。このBSRには、さまざまなバウンダリスキャンの「セル」が含まれています。通常、これらのバウンダリスキャンセルは表示されませんが、テストモード内でデバイスピンから値を設定または読み取るために使用できます。

TAPまたはテストアクセスポートと呼ばれるJTAGインターフェイスは、TCK、TMS、TDI、TDO、TRSTなどのバウンダリスキャン操作をサポートするためにさまざまな信号を使用します。

- TCKまたはテストクロック信号は、ステートマシンの内部動作を単に同期します。

- TMSまたはテストモード選択信号は、次の状態を決定するためにテストクロック信号の立ち上がりエッジでサンプリングされます。

- TDIまたはテストデータ入力信号は、テストデバイスにシフトされたデータを示します。それ以外の場合はプログラミングロジックです。内部ステートマシンが適切な状態になると、TCKの増加エッジでサンプリングされます。

- TDOまたはテストデータ出力信号は、テストデバイスのシフトアウトされたデータを示します。それ以外の場合はプログラミングロジックです。内部ステートマシンが正しい状態になると、TCKの減少エッジで有効になります。

- TRSTまたはテストリセットは、TAPコントローラーのステートマシンをリセットするために使用されるオプションのピンです。

TAPコントローラー

JTAGのアーキテクチャのテストアクセスポイントは、TAPコントローラ、命令レジスタ、およびテストデータレジスタで構成されています。このコントローラーには、TMSおよびTCK信号の読み取りを担当するテストステートマシンが含まれています。ここで、データi / pピンは、ICコアと物理ピンの間の境界セルにデータをロードするために使用されます。また、データレジスタの1つまたは命令レジスタにデータをロードするためにも使用されます。データo/pピンは、レジスタまたは境界セルからデータを読み取るために使用されます。

TAPコントローラーのステートマシンはTMSによって制御され、TCKによってクロックされます。ステートマシンは、命令モードとデータモードのような2つの異なるモードを示すために2つのパスを使用します。

レジスター

バウンダリスキャンで使用できるレジスタは2種類あります。すべての準拠デバイスには、最小2つ以上のデータレジスタと1つの命令レジスタが含まれています。

命令レジスタ

命令レジスタは、現在の命令を保持するために使用されます。そのため、そのデータは、取得された信号で何を実行するかを決定するためにTAPコントローラーによって使用されます。ほとんどの場合、命令レジスタデータは、どのデータレジスタに信号を渡す必要があるかを記述します。

データレジスタ

データレジスタには、BSR(バウンダリスキャンレジスタ)、BYPASS、IDCODESレジスタの3種類があります。また、他のデータレジスタが存在する場合もありますが、JTAG標準の要素としては必要ありません。

バウンダリスキャンレジスタ(BSR)

BSRは、デバイスのI/Oピンとの間でデータをシフトするために使用されるメインのテストデータレジスタです。

バイパス

バイパスは、TDI –TDOからデータを渡すために使用されるシングルビットレジスタです。そのため、回路内の追加のデバイスを最小限のオーバーヘッドでテストできます。

IDコード

このタイプのデータレジスタには、デバイスのIDコードとリビジョン番号が含まれています。したがって、このデータにより、デバイスをBSDL(境界スキャン記述言語)ファイルに接続できます。このファイルには、デバイスのバウンダリスキャン構成の詳細が含まれていました。

JTAGの動作は、最初は命令モードが選択され、このモードの「パス」の状態の1つにより、オペレーターはTDIによる命令内でクロックを供給できます。その後、ステートマシンは再配置されるまで開発されます。ほとんどの命令の次のステップは、データモードを選択することです。したがって、このモードでは、データはTDIを介してロードされ、TDOから読み取られます。 TDIおよびTDOの場合、データパスは、クロックインされた命令に従って配置されます。読み取り/書き込み操作が完了すると、ステートマシンは再びリセット状態になります。

JTAGとUARTの違い

JTAGとUARTの違いは次のとおりです。

| JTAG |

UART |

| 「JTAG」という用語は、Joint TestActionGroupの略です。 | 用語 ' UART 」はUniversalAsynchronousReceiver/Transmitterの略です。 |

| フラッシュのプログラミングに内蔵ハードウェアを利用する同期インターフェースです 。 | UARTは、メモリ内で実行されるブートローダーを利用する非同期インターフェイスです。 |

| これは、デバッグに使用されるテストポートのセットですが、ファームウェアのプログラムにも使用できます(これは一般的に行われます)。

|

UARTは、マイクロコントローラー、ROM、RAMなどのデバイスとの間の通信を制御するタイプのチップです。ほとんどの場合、デバイスとの通信を可能にするのはシリアル接続です。 |

| これらは、TDI、TDO、TCK、TMS、およびTRSTの4つのタイプで利用できます。 | これらは、ダムUARTとFIFOUARTの2つのタイプで利用できます。 |

| 共同テストアクショングループは、マイクロコントローラと関連デバイスのインターフェイスで使用されるシリアルプログラミングまたはデータアクセスプロトコルです。 | UARTは、RS-232/RS-485のような非同期シリアルストリームを生成するためのハードウェアを提供するために使用されるマイクロコントローラーのサブコンポーネントの一種です。 |

| JTAGコンポーネントは、プロセッサ、FPGA、 CPLD 、など | UARTコンポーネントは、CLKジェネレータ、I / Oシフトレジスタ、送信または受信バッファ、システムデータバスバッファ、読み取りまたは書き込み制御ロジックなどです。 |

JTAGプロトコルアナライザー

PGY-JTAG-EX-PDのようなJTAGプロトコルアナライザは、ホストとテスト対象の設計の間の通信をキャプチャおよびデバッグするためのいくつかの機能を含むプロトコルアナライザの一種です。このタイプのアナライザは、マスターやスレーブなどのPGY-JTAG-EX-PDを配置してJTAGトラフィックを生成し、のデコードパケットをデコードすることで、テストおよび設計エンジニアがJTAGの特定の設計の仕様をテストできるようにする主要な機器です。共同テストアクショングループプロトコル。

特徴

JTAGプロトコルアナライザの機能は次のとおりです。

- 最大25MHのJTAG周波数をサポートします。

- バスのJTAGトラフィックとプロトコルデコードを同時に生成します。

- JTAGマスター機能があります。

- 可変JTAGデータ速度とデューティサイクル。

- ユーザー定義のTDIおよびTCK遅延。

- ホストコンピュータのUSB2.0または3.0インターフェイス。

- プロトコルデコード内のエラー分析

- プロトコルデコードバスタイミング図。

- 大きなバッファを提供するためのホストコンピュータへの継続的なプロトコルデータストリーミング。

- プロトコルアクティビティリスト。

- さまざまな速度で、複数のデータフレーム生成を組み合わせるための演習スクリプトを作成できます。

タイミング図

The JTAGのタイミング図 プロトコルを以下に示します。次の図では、TDOピンは、shift-IR / shift-DRコントローラーの状態を除いて、高インピーダンス状態のままです。

shift-IRおよびShift-DRコントローラーの状態では、TDOピンはターゲットを介したTCKの減少エッジで更新され、ホストを介したTCKの増加エッジでサンプリングされます。

TDIピンとTMSピンの両方は、ターゲットを介してTCKの増加するエッジで単純にサンプリングされます。立ち下がりエッジで更新されます。それ以外の場合は、ホストを介してTCKします。

アプリケーション

The JTAGアプリケーション 以下のものが含まれます。

- 共同テストアクショングループは、エミュレーションまたはデバッグ機能へのエントリの権利を提供するためにプロセッサで頻繁に使用されます。

- すべてのCPLDおよびFPGAは、これをインターフェイスとして使用して、プログラミング機能にアクセスできるようにします。

- 物理的なアクセスなしでPCBテストに使用されます

- ボードレベルの製造テストに使用されます。

したがって、これはすべてについてです JTAGの概要 –ピン構成、アプリケーションでの作業。業界標準のJTAGは、設計検証と製造後のPCBテストに使用されます。ここにあなたへの質問があります、JTAGはの略ですか?