に デジタル-アナログコンバーター (( ダキア人 、 D / A 、 D2A 、または D-to-A )は、デジタル入力信号をアナログ出力信号に変換するように設計された回路です。アナログ-デジタルコンバータ(ADC)は逆の方法で動作し、アナログ入力信号をデジタル出力に変換します。

この記事では、図と式を使用して、デジタル-アナログ、およびアナログ-デジタルコンバータ回路がどのように機能するかを包括的に説明します。

エレクトロニクスでは、電圧と電流がさまざまな範囲と大きさで連続的に変化することがあります。

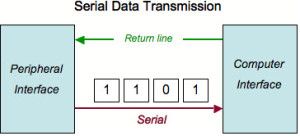

デジタル回路では、電圧信号は2つの形式で、論理高または論理低のいずれかの論理レベルであり、1または0のバイナリ値を表します。

アナログ-デジタルコンバーター(ADC)では、入力アナログ信号はデジタルマグニチュードとして表され、デジタルアナログコンバーター(DAC)はデジタルマグニチュードをアナログ信号に変換します。

デジタル-アナログコンバーターのしくみ

デジタルからアナログへの変換プロセスは、さまざまな手法で実行できます。

よく知られている方法の1つは、ラダーネットワークと呼ばれる抵抗器のネットワークを利用する方法です。

ラダーネットワークは、通常0 VまたはVrefのバイナリ値を含む入力を受け入れるように設計されており、バイナリ入力の大きさに相当する出力電圧を供給します。

次の図は、4ビットのデジタルデータとDC電圧出力を表す4つの入力電圧を使用するラダーネットワークを示しています。

出力電圧は、次の式で表されるデジタル入力値に比例します。

上記の例を解くと、次の出力電圧が得られます。

ご覧のとおり、0110のデジタル入力二6Vのアナログ出力に変換されます。

ラダーネットワークの目的は、16の潜在的なバイナリの大きさを変更することです

Vの間隔で16の電圧量の1つに0000から1111までref/ 16。

したがって、より多くのラダーユニットを含めることにより、より多くのバイナリ入力を処理し、各ステップでより高い量子化を実現できる可能性があります。

つまり、10ステップのラダーネットワークを使用すると、電圧ステップの量または分解能をVに上げることができます。ref/二10またはVref/ 1024。この場合、基準電圧Vを使用した場合ref= 10 Vは、10 V / 1024のステップで、または約10mVで出力電圧を生成します。

したがって、ラダーステージの数を増やすと、それに比例して解像度が高くなります。

通常、 n ラダーステップの数。これは次の式で表すことができます。

Vref/ 二n

DACブロック図

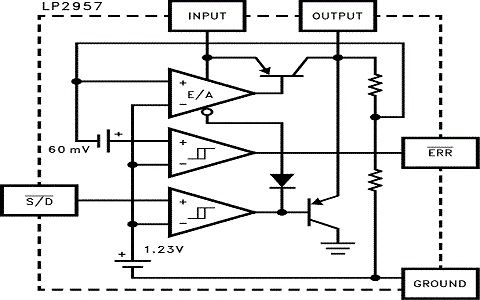

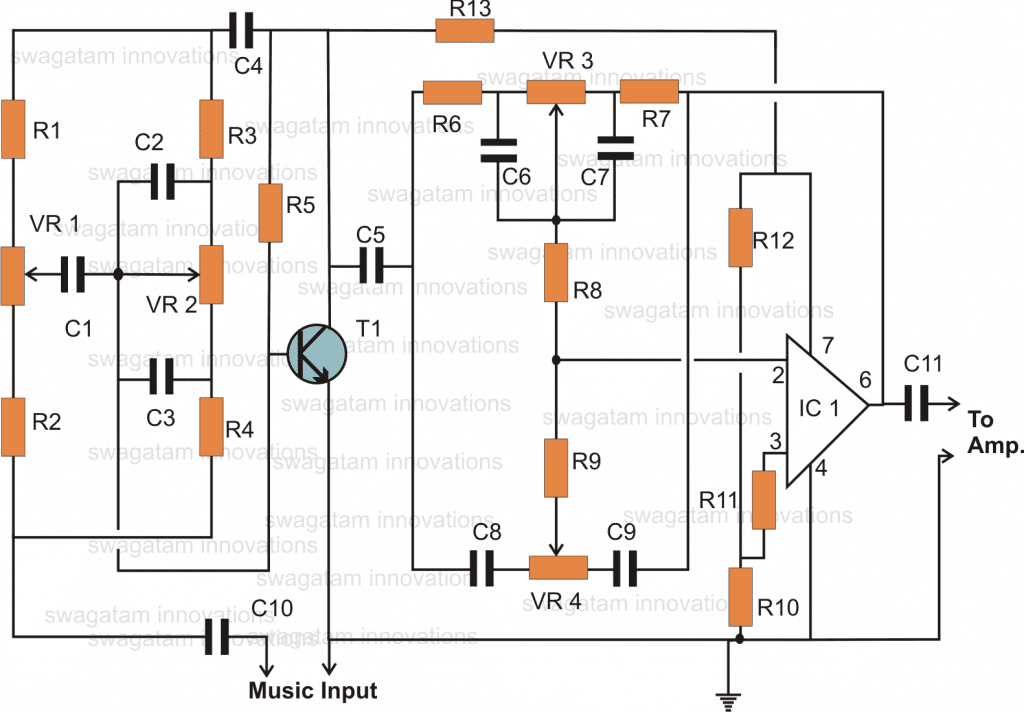

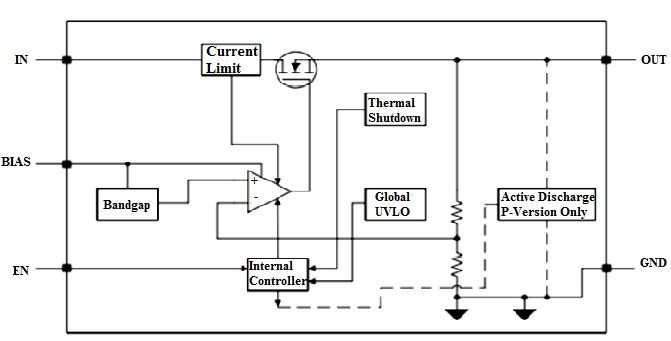

次の図は、R-2Rラダーと呼ばれるラダーネットワークを使用した標準DACのブロック図を示しています。これは、基準電流源と電流スイッチの間でロックされていることがわかります。

電流スイッチはバイナリスイッチとリンクしており、入力バイナリ値に比例した出力電流を生成します。

バイナリ入力はラダーのそれぞれのレッグを切り替え、電流リファレンスの加重和である出力電流を有効にします。

必要に応じて、結果をアナログ出力として解釈するための抵抗を出力に接続できます。

アナログ-デジタルコンバーターのしくみ

これまで、デジタル信号をアナログ信号に変換する方法について説明してきましたが、今度はその逆、つまりアナログ信号をデジタル信号に変換する方法を学びましょう。これは、と呼ばれるよく知られた方法で実装できます。 デュアルスロープ法 。

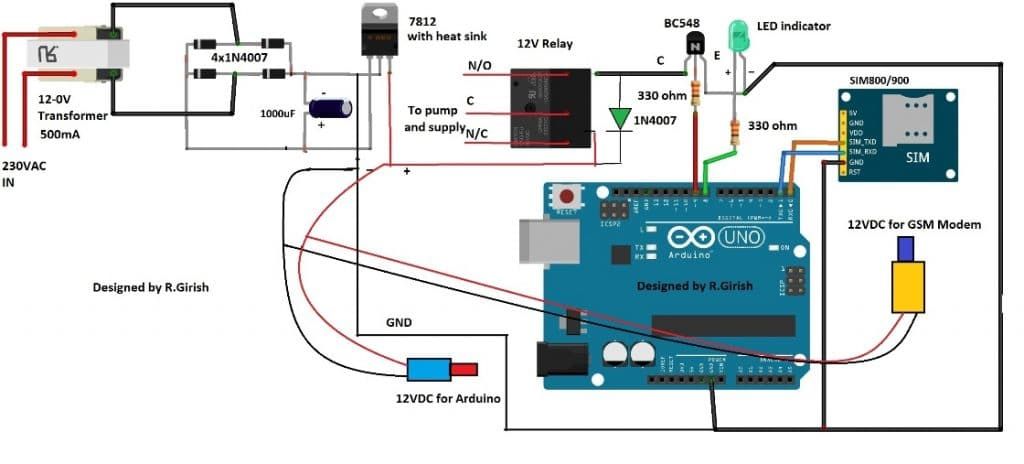

次の図は、標準のデュアルスロープADCコンバータのブロック図を示しています。

ここでは、電子スイッチを使用して、ランプジェネレータとも呼ばれる積分器に目的のアナログ入力信号を転送します。このランプ発生器は、線形ランプを生成するために定電流で充電されたコンデンサの形をとることができる。これにより、積分器の正と負の両方のスロープ間隔で機能するカウンターステージを介して必要なデジタル変換が生成されます。

この方法は、以下の説明で理解できます。

カウンタの全測定範囲が固定時間間隔を決定します。この間隔では、積分器に入力アナログ電圧が印加されると、コンパレータの入力電圧が正のレベルまで上昇します。

上の図の(b)セクションを参照すると、一定の時間間隔の終了時の積分器からの電圧が、大きさが大きい入力電圧よりも高いことがわかります。

固定時間間隔が終了すると、カウントが0に設定され、電子スイッチに積分器を固定基準入力電圧レベルに接続するように促します。この後、コンデンサの入力でもある積分器の出力は一定の速度で低下し始めます。

この期間中、カウンタは前進し続けますが、積分器の出力は、コンパレータの基準電圧を下回るまで一定の速度で低下し続けます。これにより、コンパレータ出力の状態が変化し、制御ロジックステージがトリガーされてカウントが停止します。

カウンタ内に保存されたデジタル振幅は、コンバータのデジタル出力になります。

正と負の両方のスロープ間隔で共通のクロックと積分器ステージを使用すると、クロック周波数のドリフトと積分器の精度制限を制御するための何らかの補償が追加されます。

基準入力値とクロックレートを適切に設定することにより、ユーザーの好みに応じてカウンタ出力をスケーリングできる場合があります。必要に応じて、カウンターをバイナリ、BCD、またはその他のデジタル形式にすることができます。

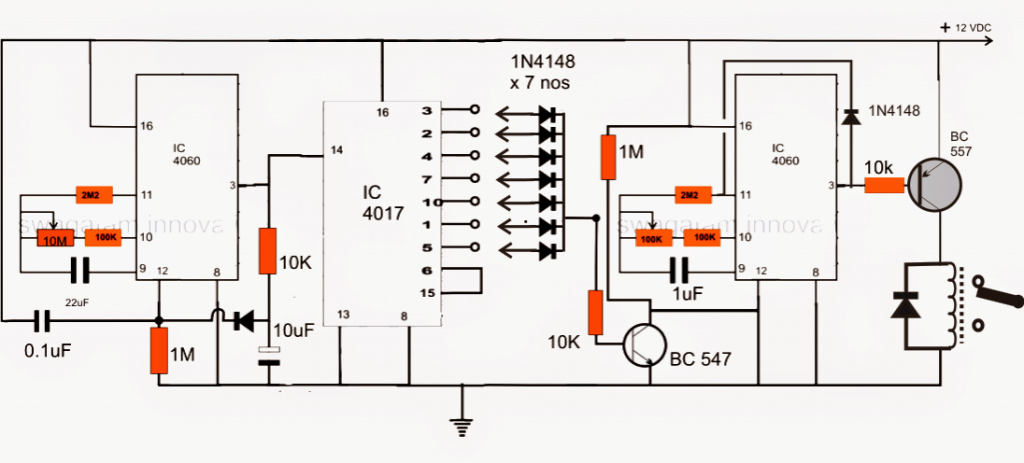

ラダーネットワークの使用

カウンタステージとコンパレータステージを使用するラダーネットワーク方式は、アナログ-デジタル変換を実装するためのもう1つの理想的な方法です。この方法では、カウンターがゼロからカウントを開始し、ラダーネットワークを駆動して、階段のように段階的な増分電圧を生成します(下の図を参照)。

このプロセスにより、カウントステップごとに電圧を上げることができます。

コンパレータは、この増加する階段電圧を監視し、アナログ入力電圧と比較します。コンパレータがアナログ入力を超える階段電圧を検出するとすぐに、その出力はカウントを停止するように促します。

この時点でのカウンタ値は、アナログ信号のデジタル等価物になります。

階段信号のステップによって生成される電圧の変化のレベルは、使用されるカウントビットの量によって決定されます。

たとえば、10 Vリファレンスを使用する12ステージのカウンタは、次のステップ電圧で10ステージのラダーネットワークを動作させます。

Vref/二12= 10 V / 4096 = 2.4 mV

これにより、2.4mVの変換分解能が作成されます。変換の実行に必要な時間は、カウンタのクロックレートによって決まります。

12ステージカウンタの動作に1MHzのクロックレートを使用する場合、変換にかかる最大時間は次のようになります。

4096x1μs=4096μs≈4.1ms

1秒あたりに可能な最小の変換数は、次のようになります。

番号。変換数= 1/4.1ms≈244変換/秒

変換プロセスに影響を与える要因

一部の変換ではより高いカウント時間が必要な場合と、より短いカウント時間が必要な場合があることを考慮すると、通常、変換時間= 4.1ms / 2 = 2.05msが適切な値になります。

これにより、平均して2 x 244 = 488のコンバージョン数が生成されます。

クロックレートが遅いと、1秒あたりのコンバージョン数が少なくなります。

カウントステージの数が少ない(解像度が低い)コンバーターは、変換率が高くなります。

コンバーターの精度は、コンパートメントの精度によって決まります。

前:フェライトコアトランスの計算方法 次へ:超音波燃料レベルインジケーター回路