NAND、NORなどの論理ゲートは、論理演算を実行するための日常のアプリケーションで使用されます。ゲートは、BJT、ダイオード、FETなどの半導体デバイスを使用して製造されています。さまざまなゲートが集積回路を使用して構築されています。デジタル論理回路は、特定の回路技術または論理ファミリに応じて製造されます。さまざまなロジックファミリは、RTL(抵抗トランジスタロジック)、DTL(ダイオードトランジスタロジック)、TTL(トランジスタ-トランジスタロジック)、ECL(エミッタ結合論理)、およびCMOS(相補型金属酸化物半導体ロジック)です。これらのうち、RTLとDTLはめったに使用されません。この記事では、 トランジスタ-トランジスタロジックまたはTTL 。

トランジスタ-トランジスタロジックの歴史

TTLまたはTransistor-TransistorLogicロジックは、1961年に「TRWのJames L.Buie」によって発明されました。新しい集積回路の開発に適しています。このTTLの実際の名前はTCTLで、これはトランジスタ結合トランジスタロジックを意味します。 1963年、製造初の商用TTLデバイスは、SUHLまたは「SylvaniaUniversal High-LevelLogicfamily」として知られる「Sylvania」によって設計されました。

テキサスインスツルメンツのエンジニアが1964年に軍用温度の範囲で5400シリーズICを発売した後、トランジスタ-トランジスタロジックは非常に人気がありました。その後、1966年に7400シリーズがより狭い範囲で発売されました。

テキサスインスツルメンツが発売した7400ファミリの互換性のある部品は、National Semiconductor、AMD、Motorola、Intel、Fairchild、Signetics、Intersil、Mullard、SGS-Thomson、Siemens、Rifaなどのいくつかの企業によって設計されました。 IBMのような会社は、独自に使用するためにTTLを使用する互換性のない回路を立ち上げました。

トランジスタ-トランジスタロジックは、約20年間にわたって速度と電力使用率を徐々に改善することにより、多くのバイポーラロジック世代に適用されました。通常、各TTLチップには数百のトランジスタが含まれています。一般に、単一のパッケージ内の機能は、論理ゲートからマイクロプロセッサまでの範囲です。

Kenbak-1のような最初のPCは、マイクロプロセッサの代替としてCPUにトランジスタ-トランジスタロジックを使用していました。 1970年には、Datapoint 2200はTTLコンポーネントを使用し、8008以降のx86命令セットのベースとなりました。

1973年にXeroxaltoによって導入されたGUIと1981年にStarワークステーションが使用されたTTL回路は、ALUのレベルで組み込まれています。

Transistor-Transistor Logic(TTL)とは何ですか?

トランジスタ-トランジスタロジック(TTL)は、BJT(バイポーラ接合トランジスタ)で構成されるロジックファミリです。名前が示すように、トランジスタは論理と増幅のような2つの機能を実行します。 TTLの最良の例は、論理ゲート、つまり7402NORゲートと7400NANDゲートです。

TTLロジックには、複数のエミッタと複数の入力を持つ複数のトランジスタが含まれています。 TTLまたはトランジスタ-トランジスタロジックのタイプには、主に標準TTL、高速TTL、ショットキーTTL、高電力TTL、低電力TTL、および高度なショットキーTTLが含まれます。

TTL論理ゲートの設計は、抵抗とBJTを使用して行うことができます。宇宙用途向けの耐放射線性TTLパッケージや、速度と低消費電力の優れた組み合わせを提供できる低電力ショットキーダイオードなど、さまざまな目的で開発されたTTLのバリエーションがいくつかあります。

トランジスタの種類-トランジスタロジック

TTLにはさまざまなタイプがあり、その分類は次のような出力に基づいて行われます。

- 標準TTL

- 高速TTL

- ショットキーTTL

- ハイパワーTTL

- 低電力TTL

- 高度なショットキーTTL。

低電力TTLは33nsのスイッチング速度で動作し、1mWのような消費電力を削減します。現在、これはCMOSロジックによって置き換えられました。高速TTLは、6nsのような通常のTTLと比較してスイッチングが高速です。ただし、22mWのような高い消費電力があります。

ショットキーTTLは1969年に発売され、ゲート端子にショットキーダイオードクランプを使用することにより、電荷の蓄積を回避してスイッチング時間を向上させるために使用されます。これらのゲート端子は3nsで動作しますが、19mWのような高い消費電力が含まれています

低電力TTLは、低電力TTLからの高抵抗値を使用します。ショットキーダイオードは、速度と2mWのような電力使用率の低下をうまくブレンドします。これは最も一般的なタイプのTTLであり、マイクロコンピューター内のグルーロジックのように使用され、基本的にL、H、Sなどの過去のサブファミリーに取って代わります。

高速TTLは、低から高への遷移を増やすために使用されます。これらの家族は、それぞれ4pJと10pJのPDPを達成しました。 3.3V電源およびメモリインターフェイス用のLVTTLまたは低電圧TTL。

ほとんどの設計者は、商用および広範な温度範囲を提供します。たとえば、Texas Instrumentsの7400シリーズ部品の温度範囲は0〜70°Cであり、5400シリーズの温度範囲は-55〜 + 125°Cです。 SNJ54シリーズの放射線装置が宇宙用途で使用されているのに対し、高い信頼性と特別な品質を備えた部品は、航空宇宙および軍事用途にアクセスできます。

TTLの特徴

TTLの特徴は次のとおりです。

- 扇形に広がります: GATEの出力が通常のパフォーマンスに影響を与えることなく駆動できる負荷の数。負荷とは、特定のゲートの出力に接続された別のゲートの入力に必要な電流の量を意味します。

- 電力損失: これは、デバイスに必要な電力量を表します。 mWで測定されます。これは通常、供給電圧と出力が高いまたは低いときに引き出される平均電流の量の積です。

- 伝播遅延: 入力レベルが変化したときに経過する遷移時間を表します。出力が遷移するために発生する遅延は、伝搬遅延です。

- ノイズマージン: これは、標準出力に影響を与えない、入力で許容されるノイズ電圧の量を表します。

トランジスタの分類-トランジスタロジック

これは、完全にトランジスタで構成される論理ファミリです。複数のエミッタを備えたトランジスタを採用しています。商業的には、7404、74S86などの74シリーズから始まります。1961年にJames L Buiによって構築され、1963年に論理設計で商業的に使用されました。TTLは出力に基づいて分類されます。

オープンコレクター出力

主な機能は、出力がローのときは0で、ハイのときはフローティングであるということです。通常、外部Vccを適用できます。

トランジスタのオープンコレクタ出力-トランジスタロジック

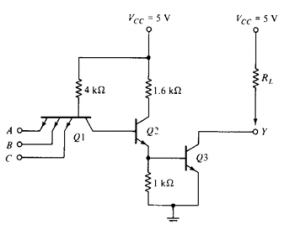

トランジスタQ1は、背中合わせに配置されたダイオードのクラスターとして動作します。入力のいずれかがロジックローの場合、対応するエミッタ-ベース接合は順方向にバイアスされ、Q1のベースの両端の電圧降下は約0.9Vであり、トランジスタQ2とQ3が導通するには不十分です。したがって、出力はフローティングまたはVcc、つまり高レベルのいずれかです。

同様に、すべての入力がハイの場合、Q1のすべてのベース-エミッタ接合は逆バイアスされ、トランジスタQ2とQ3は十分なベース電流を取得し、飽和モードになります。出力はロジックローです。 (トランジスタが飽和状態になるには、コレクタ電流がベース電流のβ倍より大きくなければなりません)。

アプリケーション

オープンコレクタ出力の用途は以下のとおりです。

- ランプやリレーの駆動に

- ワイヤード論理接続の実行

- 共通バスシステムの構築において

トーテムポール出力

トーテムポールとは、ゲートの出力にアクティブなプルアップ回路を追加することを意味します。これにより、伝搬遅延が減少します。

トーテムポール出力TTL

論理演算はオープンコレクタ出力と同じです。トランジスタQ4とダイオードの使用は、Q3の両端の寄生容量の急速充電と放電を提供することです。抵抗は、出力電流を安全な値に保つために使用されます。

スリーステートゲート

次のような3ステート出力を提供します

- 下位トランジスタがオンで上位トランジスタがオフの場合の低レベル状態。

- 下のトランジスタがオフで上のトランジスタがオンのときのハイレベル状態。

- 両方のトランジスタがオフの場合の3番目の状態。それ 直接配線接続が可能 多くの出力の。

スリーステートゲートトランジスタ-トランジスタロジック

TTLファミリの機能

TTLファミリの機能は次のとおりです。

- ロジックローレベルは0または0.2Vです。

- ロジックハイレベルは5Vです。

- 10個中の典型的なファン。これは、出力で最大10個のゲートをサポートできることを意味します。

- 基本的なTTLデバイスは約10mWの電力を消費しますが、ショットキーデバイスを使用すると電力が減少します。

- 平均伝搬遅延は約9nsです。

- ノイズマージンは約0.4Vです。

TTLICシリーズ

TTLICは主に7シリーズから始まります。次のように指定された6つのサブファミリーがあります。

- 35nsの伝搬遅延と1mWの消費電力を備えた低電力デバイス。

- 低電力ショットキー 9nsの遅延のあるデバイス

- 1.5nsの遅延を持つ高度なショットキーデバイス。

- 高度な低電力ショットキー 4nsの遅延と1mWの電力損失を持つデバイス。

TTLデバイスの命名法では、最初の2つの名前は、デバイスが属するサブファミリーの名前を示します。最初の2桁は、動作温度範囲を示します。次の2つのアルファベットは、デバイスが属するサブファミリーを示します。最後の2桁は、チップによって実行される論理機能を示します。例は、74LS02-2入力NORゲート、74LS10-トリプル3入力NANDゲートです。

典型的なTTL回路

論理ゲートは、衣類乾燥機、コンピュータープリンター、ドアベルなどのアプリケーションで日常生活で使用されます。

TTLロジックを使用して実装された3つの基本的なロジックゲートを以下に示します。

NORゲート

入力Aがロジックハイで、対応するトランジスタのエミッタ-ベース接合が逆バイアスされ、ベース-コレクタ接合が順バイアスされているとします。トランジスタQ3は電源電圧Vccからベース電流を取得し、飽和状態になります。 Q3からのコレクタ電圧が低いため、トランジスタQ5は遮断されますが、別の入力が低い場合は、Q4が遮断され、それに応じてQ5が遮断され、出力はトランジスタQ3を介して直接グランドに接続されます。 。同様に、両方の入力がロジックローの場合、出力はロジックハイになります。

NORゲートTTL

ゲートではありません

入力が低い場合、対応するベース-エミッタ接合は順方向にバイアスされ、ベース-コレクタ接合は逆方向にバイアスされます。その結果、トランジスタQ2が遮断され、トランジスタQ4も遮断される。トランジスタQ3が飽和状態になり、ダイオードD2が導通を開始し、出力がVccに接続され、ロジックハイになります。同様に、入力がロジックハイの場合、出力はロジックローになります。

ゲートTTLではありません

他のロジックファミリとのTTL比較

一般に、TTLデバイスはCMOSデバイスと比較してより多くの電力を使用しますが、電力使用率はCMOSデバイスのクロック速度によって向上しません。現在のECL回路と比較すると、トランジスタ-トランジスタロジックは低電力を使用しますが、設計ルールは単純ですが、大幅に低速です。

メーカーは、同じシステム内でTTLデバイスとECLデバイスを統合して最高のパフォーマンスを実現できますが、2つのロジックファミリ間でレベルシフトなどのデバイスが必要です。 TTLは、初期のCMOSデバイスと比較して、静電放電による損傷の影響を受けにくいです。

TTLデバイスのo / p構造により、o / pインピーダンスは低状態と高状態の間で非対称であり、伝送ラインの駆動には不適切です。通常、この欠点は、信号がケーブル全体に送信する必要がある場合は常に、特別なラインドライバデバイスを使用してo / pをバッファリングすることで克服されます。

TTLのトーテムポールo / p構造は、高位トランジスタと低位トランジスタの両方が導通するとすぐにオーバーラップすることが多く、その結果、電源から実質的な電流信号が引き出されます。

これらの信号は、いくつかのICパッケージ間で突然接続される可能性があり、その結果、パフォーマンスが低下し、ノイズマージンが減少します。一般に、TTLシステムはそれぞれにデカップリングコンデンサを使用します。それ以外の場合は2つのICパッケージを使用するため、1つのTTLチップからの電流信号によって電圧供給電圧が瞬間的に低下することはありません。

現在、多くの設計者は、同じピン配列を含む対応するTTLコンポーネントに関連する部品番号を通じて、TTL互換のi / pおよびo / pレベルを通じて同等のCMOSロジックを提供しています。したがって、たとえば、74HCT00シリーズは、7400バイポーラシリーズ部品にいくつかのドロップイン代替品を提供しますが、CMOSテクノロジを利用します。

異なる仕様に関するTTLと他のロジックファミリの比較には、次のものが含まれます。

| 仕様 | TTL | CMOS | ECL |

| ベーシックゲート | NAND | NOR / NAND | OR / NOR |

| コンポーネント | 受動素子とトランジスタ | MOSFET | 受動素子とトランジスタ |

| 扇形に広がります | 10 | > 50 | 25 |

| ノイズ耐性 | 強い | 非常に強い | 良い |

| ノイズマージン | 中程度 | 高い | 低 |

| ns単位のTPD | 1.5から30 | 1から210 | 1から4 |

| MHz単位のクロックレート | 35 | 10 | > 60 |

| mWattの電源/ゲート | 10 | 0.0025 | 40から55 |

| 性能指数 | 100 | 0.7 | 40から50

|

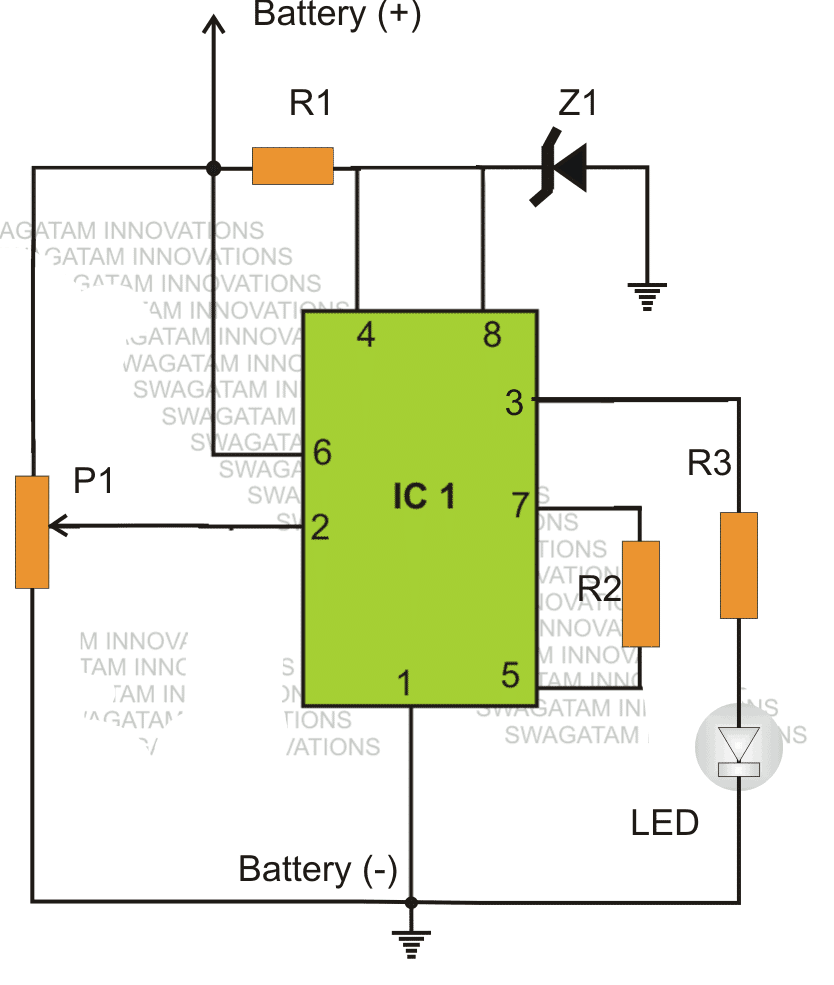

トランジスタ-トランジスタロジックインバーター

トランジスタトランジスタロジック(TTL)デバイスは、動作が速く、機能が安価であるため、ダイオードトランジスタロジック(DTL)に取って代わりました。クワッド2入力のNANDICは、7400 TTLデバイスを使用して、インバーターとして使用される幅広い回路を設計します。

上の回路図は、IC内でNANDゲートを使用しています。したがって、スイッチAを選択して回路をアクティブにすると、回路の両方のLEDがオフになることがわかります。出力が低い場合、入力は高いはずです。その後、スイッチBを選択すると、両方のLEDが点灯します。

スイッチAが選択されると、NANDゲートの両方の入力がハイになります。これは、論理ゲートの出力が少なくなることを意味します。スイッチBを選択すると、入力が長時間ハイにならず、LEDがオンになります。

長所と短所

TTLのデメリットのメリットは次のとおりです。

TTLの主な利点は、他の回路と簡単にインターフェースできることと、特定の電圧レベルと優れたノイズマージンのために難しい論理関数を生成できることです。TTLには、ファンインなどの優れた機能があります。これは、i / p信号の数を意味します。入力を介して受け入れることができます。

TTLは主に、CMOSとは異なり、定常的な放電による害の影響を受けません。CMOSと比較すると、これらは経済的です。 TTLの主な欠点は、電流使用率が高いことです。 TTLの高い電流要求は、o / p状態がオフになるため、不快な機能につながる可能性があります。消費電流が少ない異なるTTLバージョンでも、CMOSと競合します。

CMOSの登場により、TTLアプリケーションはCMOSに置き換えられました。ただし、TTLは非常に堅牢で、論理ゲートがかなり安価であるため、アプリケーションで引き続き使用されます。

TTLアプリケーション

TTLのアプリケーションは次のとおりです。

- 0〜5Vを提供するためのコントローラーアプリケーションで使用されます

- ランプやリレーを駆動する際のスイッチングデバイスとして使用されます

- のプロセッサで使用されます ミニコンピューター DECVAXのように

- プリンターやビデオディスプレイ端末で使用

したがって、これはすべてについてです TTLまたはトランジスタ-トランジスタロジックの概要 。これは、論理状態を維持し、BJTを使用してスイッチングを実現するICのグループです。 TTLは、TTLやDTLに比べて安価で、高速で、信頼性が高いため、ICが広く使用されている理由の1つです。 TTLは、複数の入力を持つゲートの複数のエミッタを介してトランジスタを使用します。ここで、あなたへの質問があります、トランジスタ-トランジスタロジックのサブカテゴリは何ですか?