投稿では、IC4043のピン配置機能とその他の重要な仕様について説明しています。この非常に興味深いチップの完全なデータシートについて学びましょう。

IC4043のピン配置データシート

技術的には、IC 4043は、3つのロジック状態出力を備えたクアッドセット/リセット(R / S)ラッチです。

より正確には、このチップには4セットの入力(8つの入力ピン配列を意味する)と4つの対応する単一出力があります。

4セットの入力は、4ペアのセット/リセット入力で構成されます。

セット/リセットごとに、対応する出力が1つあります。

これらのセットリセット入力はすべてハイロジック信号に応答し、対応する出力ピン配置で双安定効果を生み出します。

双安定フリップフロップ

双安定とは、フリップフロップ動作を指します。つまり、「セット」入力へのハイパルスは、対応する出力を元のロー状態からハイにし、リセット入力へのハイは、上記の状態をハイからロー状態に戻します。

したがって、基本的に対応する出力をHighにするには、「set」入力にHighを適用し、出力を再びLowにするには、リセット入力に別のHighを適用する必要があります。

入力ピン配列と出力ピン配列の機能はそれと同じくらい簡単です。

これに加えて、ICには、共通の出力イネーブルピン配列である別の興味深い入力ピン配列OEがあります。

セット/リセット機能

ICで上記のセット/リセットアクションを有効にするには、このOE入力をロジックハイまたは単にVdd(電源電圧)に接続する必要があります。

上記の状況では、指定されたフリップフロップが機能している状態で出力が許可されます。

OE入力がグランドに接続されている場合、出力はフリーズして高インピーダンス応答を生成します。これは、低出力も高出力も示さず、入力を無応答のブロック状態にロックするため、名前3の論理状態出力になります。

したがって、特定のアプリケーションで必要な場合は、OE入力を使用してICの機能をシャットダウンできます。

このICは、5〜15Vの電源電圧で最適に動作します。

IC4043の入出力ピン配置機能と仕様を以下のデータでまとめてみましょう。

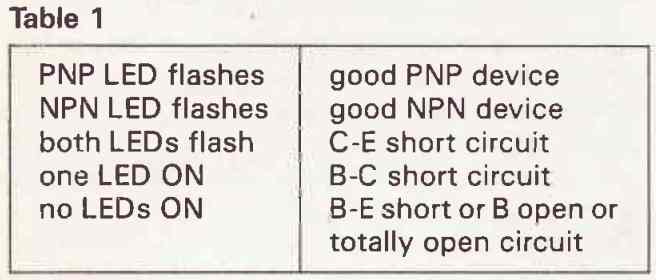

- 1Q〜4Q(ピン:2、9、10、1)トライステートバッファラッチ出力

- 1R〜4R(ピン:3、7、11、15)リセット入力(アクティブHIGH)

- 1S〜4S(ピン:4、6、12、14)セット入力(アクティブHIGH)

- OE(ピン:5)共通出力イネーブル入力

- VSS(ピン:8)接地供給電圧

- N.C.(ピン:13)が接続されていません

- VDD(ピン:16)供給電圧

その他の更新:

この投稿では、さまざまな仕様、デバイスのデータシート、およびそれらのピン配置の配置を検討することにより、IC4043およびIC4044の動作を理解しようとしています。

基本的に、両方のバリアントは、クアッドクロスカップリングされたCMOSトライステートR / Sまたはリセット/セットラッチです。クワッドとは、制御入力信号を介してロジックハイで設定またはラッチするか、後続の入力信号でロジックゼロにリセットできる4つの出力を持つことを意味します。

3ステート機能により、3ロジックを使用してICを制御できます。

IC4043とIC4044の基本的な動作原理は上記と同じですが、唯一の違いは、IC4043Bがクワッドクロスカップリングされたトライステートであるということです。 NOR ラッチ、およびIC4044Bはクワッドクロス結合トライステートです NAND ラッチ。

ピン配置図

次のICのピン配置図は、デバイスの内部構造とピン配置の詳細を示しています。

上の図では、各タイプに1つの出力と2つの個別のRESET / SET入力を備えた4つのラッチがあることがわかります。すべてのSET / RESET入力のENABLEピンの機能は同じです。

ENABLEピンのロジックHIGHにより、ラッチ状態を関連する出力に接続できます。ロジックローまたは0の場合、ラッチ状態が出力から切断され、出力間で完全な開回路が発生します。

NORラッチ、NANDラッチの等価論理図

次の図は、個々のICの4つのラッチのそれぞれの内部に存在するNORおよびNANDラッチの形式の同等のラッチを示しています。

ご覧のとおり、各ラッチブロックは、SET、RESET、およびENABLEの3つの論理制御入力を使用して制御されるため、出力はこれら3つの入力状態に依存します。これらの3つの論理状態の真理値表は、次の図から学ぶことができます。

上記の真理値表では、さまざまな省略記号のアルファベットの完全な形式は、次のように理解できます。S= SETピンR = RESETピンE = ENABLEピンQ = OUTPUTピンOC =開回路NC =変更なし

IC4043およびIC4044の主な機能を以下に要約します。

SET / RESETピンとENABLEピンの実用的な基本動作シミュレーション

作業の説明

上記のシミュレーションGIFから、クアッドラッチモジュールの動作を次の点で理解できます。

SETが正電源でピン印加されると、赤色LED(順方向バイアス)で示されるように、SETピンから正の電位が除去されても、出力はハイになり、ラッチされます。

RESETピンに正のパルスが印加されると、ラッチが壊れ、RESETピンから正の値が削除されても出力は永続的にLOWになります。これは、青色LEDの点灯によって示されます。

上記の操作は、ICのENABLEピンが正の電源電位にある場合にのみ実装できます。負またはグランド電位に接続すると、ラッチの出力が開き、SET / RESET操作に応答しなくなります。

前:平日プログラマブルタイマー回路 次へ:IC 4033のピン配列、データシート、アプリケーション