メモリは、制御に使用される情報を格納するためのマイクロコントローラまたはCPUの重要なコンポーネントです エレクトロニクスプロジェクト 。内部的には、メモリは、データの格納に役立つ特殊なタイプのレジスタで構成されるいくつかの部分に分割されています。 RAMメモリとROMメモリの2種類のメモリがあり、多くの場合、同様の方法で使用できます。ここでは、8051のRAMメモリ構成とそのレジスタについて説明します。この情報は、 組み込みシステム設計 プログラムを簡単に書くことができます。

RAMメモリ

8051マイクロコントローラーのRAMメモリ構成:

8051マイクロコントローラには256バイトのRAMメモリがあり、128バイトなどの2つの方法で分割されます。 特殊機能レジスタ (SFR)および汎用メモリ用の128バイト。 RAMメモリ構成には次のグループが含まれます 汎用レジスタ これらは固定メモリアドレスレジスタで情報を格納するために使用され、SFRメモリには「B」レジスタ、アキュムレータ、カウンタまたはタイマーなどの周辺関連レジスタと割り込み関連レジスタがすべて含まれています。

RAMメモリ構成:

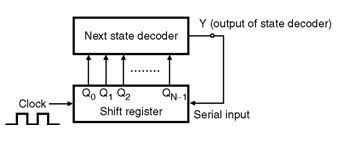

RAMメモリ内の格納場所のグループはRAMメモリ構成と呼ばれ、PSWレジスタ値によって制御できます。 8051マイクロコントローラー RAMメモリは、バンク、ビットアドレス可能領域、スクラッチパッド領域などの一連のストレージロケーションに内部的に分割されています。

RAMメモリ構成

銀行:

バンクには、R0〜R7などのさまざまな汎用レジスタが含まれており、そのようなレジスタはすべて、1バイトのデータのみを格納または削除するバイトアドレス指定可能なレジスタです。銀行は次のような4つの異なる銀行に分かれています

- Bank0

- Bank1

- Bank2

- Bank3

各バンクは8つの汎用レジスタで構成され、保存された情報を分類するための独自のアドレスを持っています。これらは、PSWレジスタの値(つまり、RS1、RS0)を使用して選択できます。 bank1、bank2、bank3はスタックポインタ領域として使用できます。スタックメモリ構成がいっぱいになると、データはスクラッチパッド領域に格納されます。スタックポインタのデフォルトアドレスは07hです。

銀行登録

ビットアドレス可能領域:

ビットアドレス可能領域は、1ビットのデータのみを格納または削除するビットアドレス可能レジスタで構成されます。このエリアには、00hから07Fhまでの合計128のアドレスがあり、データの保存場所を表します。ビットアドレス可能領域は、レジスタバンクの近くに形成されます。それらはアドレス20Hから2FHまで設計されています。主にビット変数を格納するために使用されるビットアドレス可能領域 アプリケーションプログラム 、LEDやモーター(オンとオフ)などのデバイス出力ステータスなど。このステータスを保存するために必要なのはビットアドレス可能領域のみです。このステータスを格納するためのバイトアドレス可能領域を検討すると、一部のメモリが無駄になります。

ビットアドレス可能領域

スクラッチパッドエリア:

スクラッチパッド領域は、1ビットのデータのみを格納または削除するバイトアドレス指定可能なレジスタで構成されます。ビットアドレス可能領域の近くに形成されます。それは30Hから7FHまで形成されます。モーターの方向(順方向および逆方向)などのデバイス出力ステータスの印刷など、主にアプリケーションプログラムからのバイト変数を格納するために使用されるスクラッチパッド領域。スタックポインタ領域がいっぱいになると、データはスクラッチパッド領域に保存されます。スクラッチパッド領域は80バイトのメモリで構成されています。

RAMメモリの種類:

2つに分類されるRAMメモリ 思い出の種類 SRAMやDRAMメモリなど。

SRAM(スタティックランダムアクセスメモリ):

スタティックランダムアクセスメモリは、電力が供給されている限りメモリに情報を保持するRAMの一種です。スタティックRAMは、データへのより高速なアクセスを提供し、DRAMと比較してより高価です。 SRAMを定期的に更新する必要はありません。

スタティックランダムアクセスメモリ

SRAMでは、各ビットは2つの交差結合インバーターを形成する4つのトランジスターに格納されます。さらに2つ トランジスタ–タイプ 読み取りおよび書き込み操作中にストレージセルへのアクセスを制御するために提供します。一般に、SRAMは各メモリビットを格納するために6つのトランジスタを使用します。これらのストレージセルには、「0」と「1」を表すために使用される2つの安定した状態があります。

DRAM(ダイナミックランダムアクセスメモリ):

DRAMは、データの各ビットを個別のコンデンサに格納するRAMモジュールの一種です。これは、データを格納するために必要な物理スペースが少ないため、データをメモリに格納するための熟練した方法です。

DRAMは、特定のチップサイズでより多くのデータを保持できます。 DRAMのコンデンサは、充電を維持するために常に再充電する必要があるため、DRAMはより多くの電力を必要とします。

ダイナミックランダムアクセスメモリ

各DRAMメモリチップは、格納場所またはメモリセルで構成されています。これは、アクティブ状態または非アクティブ状態のいずれかを保持できるコンデンサとトランジスタで構成されています。各DRAMセルはビットと呼ばれます。

DRAMセルがアクティブ状態のとき、充電はハイ状態です。 DRAMセルが非アクティブ状態の場合、充電は特定のレベルを下回っています。

キャッシュメモリの整理:

キャッシュメモリは、メインメモリの場所から頻繁に使用されるデータを保持するために使用されるメモリの一種です。キャッシュメモリはCPUの近くに配置されます。キャッシュメモリは00hから0Fhまで始まります。キャッシュメモリは比較的小さく、8kと16kで構成されていますが、効果的に機能します。これはバイトアドレス可能なメモリであり、1ビットのデータのみを格納および削除します。 CPUが命令を必要とするときに、メインメモリからいっぱいになるキャッシュメモリ。主にアクセスメモリへの平均時間を短縮するために使用されるキャッシュメモリ。

SRAMとDRAMの利点とアプリケーション:

SRAMの利点:

- SRAMは、オンチップメモリに大容量のストレージを提供します

- 通常、SRAMのレイテンシは非常に低く、パフォーマンスは高いです。

- 他のメモリと比較して、設計とインターフェースが非常に簡単です

DRAMの利点:

- ストレージ容量が非常に高い

- 低コストで高性能なデバイスです。

この記事では、8051マイクロコントローラのメモリ構成、RAMメモリの種類、バンクレジスタ、およびキャッシュメモリ構成について簡単に説明します。メモリ構成と技術支援に関する詳細については、 マイクロコントローラーベースのプロジェクト 、下のコメントセクションにコメントを投稿してください。