私たちの日常生活の中で、私たちはさまざまな種類の電子機器に出くわします。エレクトロニクスの生産に革命をもたらした技術の1つは「 集積回路 「。この技術は、密度を上げることによって電子製品のサイズを縮小しました 論理ゲート チップあたり。現在、さまざまなタイプと構成のICがあります。周りを観察すると、一部のICは特定のアプリケーションにのみ使用でき、一部のICは再プログラムしてさまざまなアプリケーションに使用できることがわかります。これらのタイプのICはASICと呼ばれます。しかし、それらはどのように異なりますか?それらを再プログラムするにはどうすればよいですか?一部のICを再プログラムできないのはなぜですか?これらの質問に対する答えを見つけるために飛び乗ってください。

ASIC(特定用途向け集積回路)とは何ですか?

ASICフルフォームは 特定用途向け集積回路。 これらの回路はアプリケーション固有です。特定のアプリケーション向けにカスタマイズされたIC。これらは通常、特定のアプリケーションの要件に基づいてルートレベルから設計されます。基本的なもののいくつか 特定用途向け集積回路の例 おもちゃで使用されるチップ、メモリとマイクロプロセッサのインターフェースに使用されるチップなどです。これらのチップは、これらが設計されている1つのアプリケーションでのみ使用できます。おそらく、これら ICの種類 大規模な生産が行われている製品にのみ推奨されます。 ASICはルートレベルから設計されているため、コストが高く、大量生産にのみ推奨されます。

ASICの主な利点は、回路の多数の機能ユニットが1つのチップ上に構築されるため、チップサイズが小さくなることです。最新のASICには通常32ビットが含まれています マイクロプロセッサ 、メモリブロック、ネットワーク回路など…このようなタイプのASICは、 システムオンチップ 。製造技術の発展と設計手法の研究の増加に伴い、さまざまなレベルのカスタマイズを備えたASICが開発されています。

ASICの種類

ASICは、プログラマーがチップ上で実行できるカスタマイズの量に基づいて分類されます。

ASICの種類

フルカスタム

このタイプの設計では、すべてのロジックセルが特定のアプリケーション用に調整されています。設計者は、回路のロジックセルを特別に作成する必要があります。相互接続用のすべてのマスクレイヤーはカスタマイズされています。したがって、プログラマーはチップの相互接続を変更することはできず、プログラミング中は回路レイアウトに注意する必要があります。

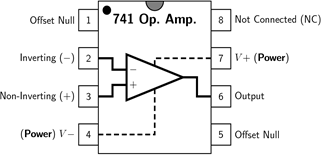

フルカスタムASICの最良の例の1つは、マイクロプロセッサです。このタイプのカスタマイズにより、設計者は単一のIC上にさまざまなアナログ回路、最適化されたメモリセル、または機械的構造を構築できます。このASICは、製造と設計にコストと非常に時間がかかります。これらのICの設計にかかる時間は約8週間です。

これらは通常、高レベルのアプリケーションを対象としています。フルカスタムデザインの主な特徴は、最大のパフォーマンス、最小の面積、最高の柔軟性です。最終的には、使用される論理セル、抵抗などの回路要素が事前にテストされていないため、設計のリスクが高くなります。

セミカスタム

このタイプの設計では、ロジックセルは標準ライブラリから取得されます。フルカスタムデザインのように手作りされていません。一部のマスクはカスタマイズされていますが、一部は事前に設計されたライブラリから取得されています。ライブラリから取得した論理セルのタイプと相互接続に許可されているカスタマイズの量に基づいて、これらのASICは、標準セルベースのASICとゲートアレイベースのASICの2つのタイプに分けられます。

1)。標準セルベースASIC

これらのICを知るために、まず標準セルライブラリの意味を理解しましょう。次のようないくつかの論理セル ANDゲート、ORゲート 、マルチプレクサ、 ビーチサンダル さまざまな構成を使用して設計者によって事前に設計され、標準化されてライブラリの形式で保存されます。このコレクションは、標準セルライブラリとして知られています。

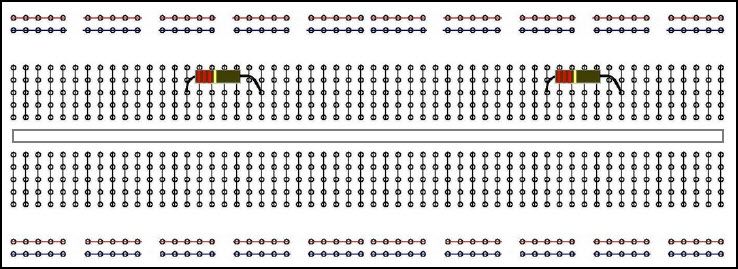

標準セルベースASIC

標準セルベースでは、これらの標準ライブラリのASICロジックセルが使用されます。 ASICチップでは、標準セル領域またはフレキシブルブロックは、行の形で配置された標準セルで構成されています。これらの柔軟なブロックに加えて、マイクロコントローラーやマイクロプロセッサーのようなメガセルがオンチップで使用されます。これらのメガセルは、メガ関数、システムレベルのマクロ、固定ブロック、機能標準ブロックとも呼ばれます。

上の図は、単一の標準セル領域と4つの固定ブロックを備えた標準セルASICを表しています。マスクレイヤーはカスタマイズされています。ここで、設計者は標準セルをダイのどこにでも配置できます。これらはC-BICとしても知られています。

2)。ゲートアレイベースのASIC

このタイプのセミカスタムASICには、事前定義があります トランジスタ シリコンウェーハ上、すなわち設計者は、ダイ上に存在するトランジスタの配置を変更することはできません。ベースアレイはゲートアレイの事前定義されたパターンであり、ベースセルはベースアレイの最小の反復セルです。

設計者は、ダイの最初の数個の金属層を使用してトランジスタ間の相互接続を変更する責任のみを負います。設計者は、ゲートアレイライブラリから選択します。これらはしばしばマスクゲートアレイと呼ばれます。ゲートアレイベースのASICには3つのタイプがあります。それらは、チャネル化ゲートアレイ、チャネルレスゲートアレイ、および構造化ゲートアレイです。

a)。チャネリングゲートアレイ

このタイプのゲートアレイでは、トランジスタの列の間に配線スペースが残されています。これらは、ブロック間の相互接続のためにスペースが残されているという点でCBICに似ていますが、チャネルゲートアレイではセル行の高さが固定されていますが、CBICではこのスペースを調整できます。

チャネリングゲートアレイ

このゲートアレイの主な機能のいくつかは次のとおりです。このゲートアレイは、相互接続のために行間に事前定義されたスペースを使用します。製造時間は2日から2週間です。

b)。チャネルレスゲートアレイ

チャネリングされたゲートアレイに見られるように、セルの行間をルーティングするための空き領域が残っていません。ここでは、メタル1とトランジスタ間の接続をカスタマイズできるため、ゲートアレイセルの上からルーティングが行われます。ルーティングでは、ルーティングのパスにあるトランジスタを未使用のままにします。製造リードタイムは約2週間です。

チャネルレスゲートアレイ

c)。構造化ゲートアレイ

このタイプのゲートアレイには、上記のようにゲートアレイ行とともに埋め込みブロックがあります。構造化ゲートアレイは、CBICのより高い面積効率を持っています。マスクされたゲートアレイのように、これらはより低いコストとより速いターンアラウンドを持っています。ここで、埋め込み関数の固定サイズは、構造化ゲートアレイに制限をもたらします。たとえば、このゲートアレイには32kビットコントローラー用に予約された領域が含まれていますが、アプリケーションで16kビットコントローラー用の領域のみが必要な場合、残りの領域は無駄になります。すべてのゲートアレイのターンアラウンドタイムは2日から2週間であり、すべてカスタマイズされた相互接続があります。

構造化ゲートアレイ

プログラム可能なASIC

プログラム可能なASICには2つのタイプがあります。 PLDとFPGAです

PLD(プログラマブルロジックデバイス)

これらは、すぐに利用できる標準セルです。 PLDをプログラムして、アプリケーションの一部をカスタマイズできるため、ASICと見なされます。 PLDをプログラムするためにさまざまな方法とソフトウェアを使用できます。これらには、フリップフロップまたはラッチとともに、通常はプログラマブルアレイロジックのロジックセルの通常のマトリックスが含まれています。ここでは、相互接続は単一の大きなブロックとして存在します。

PROMはこのICの一般的な例です。 EPROMは相互接続としてMOSトランジスタを使用しているため、高電圧を印加することでプログラムできます。 PLDには、カスタマイズされたロジックセルや相互接続はありません。これらは、設計のターンアラウンドが速いです。

プログラマブルロジックデバイス

FPGA(フィールドプログラマブルゲートアレイ)

PLDがロジックセルとしてプログラマブルアレイロジックを備えている場合 FPGA ゲートアレイのような配置になっています。 PLDはFPGAよりも小さく、複雑ではありません。その柔軟性と特性により、FPGAは置き換えられています TTL マイクロエレクトロニクスシステムで。設計の所要時間はわずか数時間です。

フィールド・プログラマブル・ゲート・アレイ

コアは、両方を実行できるプログラム可能な基本ロジックセルで構成されています 組み合わせと シーケンシャルロジック 。ロジックセルをプログラムし、いくつかの方法を使用して相互接続できます。基本的なロジックセルはプログラム可能な相互接続のマトリックスに囲まれ、コアはプログラム可能なI / Oセルに囲まれています。

FPGAは通常、構成可能なロジックブロック、構成可能なI / Oブロック、プログラム可能なインターコネクト、クロック回路、ALU、メモリ、デコーダーで構成されます。

さまざまなタイプのASICが利用可能であることを確認しました。次に、これらすべてのカスタマイズと相互接続が製造中にいつ行われるかを理解しましょう。

特定用途向け集積回路(ASIC)の設計フロー

ASICの設計は、段階的に実行されます。この手順の順序は、 ASIC設計 フロー。設計フローの手順を以下のフローチャートに示します。

ASICデザインフロー

デザインエントリー: このステップでは、VHDL、Verilog、SystemVerilogなどのハードウェア記述言語を使用してデザインのマイクロアーキテクチャを実装します。

論理合成: このステップでは、使用するロジックセルのネットリスト、相互接続のタイプ、およびアプリケーションに必要なその他すべてのパーツがHDLを使用して準備されます。

システム分割: このステップでは、大部分のサイズのダイをASICサイズのピースに分割します。

プレレイアウトシミュレーション: このステップでは、シミュレーションテストを実行して、デザインにエラーが含まれているかどうかを確認します。

フロアプラン: このステップで、ネットリストのブロックがチップ上に配置されます。

配置: このステップで、ブロック内のセルの位置が決定されます。

ルーティング: このステップでは、ブロックとセルの間に接続が描画されます。抽出:このステップでは、相互接続の抵抗値や静電容量値などの電気的特性を決定します。

レイアウト後のシミュレーション: 製造用のモデルを提出する前に、このシミュレーションを実行して、システムが相互接続の負荷とともに適切に機能するかどうかを確認します。

ASICの例

ASICのさまざまな特性を理解したところで、ASICの例をいくつか見てみましょう。

標準セルベースASIC: LCB 300k、LSI Logic Companyの500k、ABB Hafo Inc.のSIG1、2、3ファミリ、GCSPlesseyのGCS90K。

ゲートアレイ製品: Harris SemiconductorのAUA20K、National SemiconductorsのSCX6Bxx、TexasInstrumentsのTGC / TECファミリ。

PLD製品: Advanced Micro DevicesのPALファミリ、Philips SemiconductorsのGALファミリ、XC7300、およびXILINXのEPLD。

FPGA製品: XC2000、XC3000、XC4000、XILINXのXC5000シリーズ、QuickLogicのpASIC1、アルテラのMAX5000。

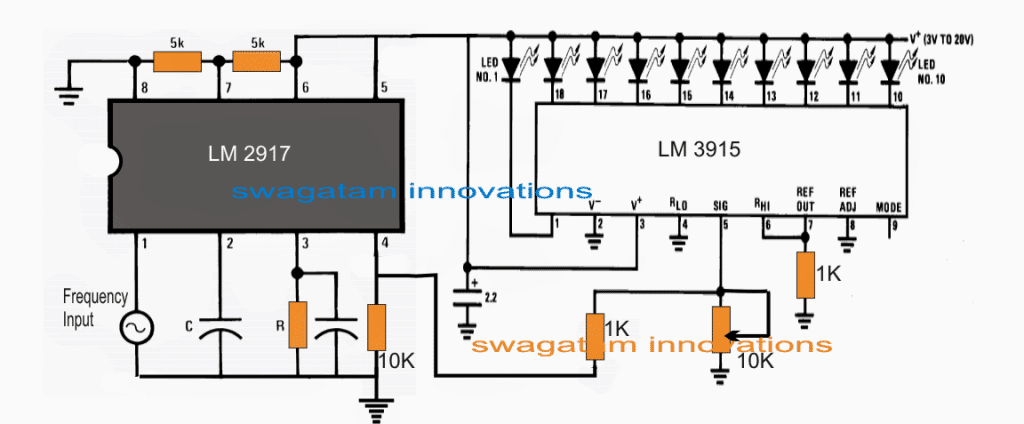

ASICのアプリケーション

ASICの独自性は、電子機器の製造方法に革命をもたらしました。これらは、密度を増加させながらダイサイズを縮小しました 論理ゲート チップあたり。 ASICは通常、高レベルのアプリケーションに適しています。 ASICチップは、衛星、ROM製造、 マイクロコントローラー 医療および研究分野でのさまざまなタイプのアプリケーション。 ASICのトレンドアプリケーションの1つは、ビットコインマイナーです。

ビットコインマイナー

暗号通貨のマイニングには、より大きな電力と高速ハードウェアが必要です。汎用CPUは、このような高い計算能力を高速で提供することはできません。 ASICビットコインマイナーは、特別に設計されたマザーボードに組み込まれたチップであり、 電源装置 、単一のユニットに構築されます。これは、ビットコインマイニング用のチップレベルまで意図的に設計されたハードウェアです。これらのユニットは、単一の暗号通貨のみのアルゴリズムを実行できます。おそらく異なるタイプの暗号通貨については、別のマイナーが必要です。

ASICの長所と短所

ザ・ ASICの利点 以下のものが含まれます。

- ASICのサイズが小さいため、洗練された大規模システムに最適です。

- 1つのチップ上に多数の回路が構築されているため、これにより高速アプリケーションが発生します。

- ASICは低消費電力です。

- それらはチップ上のシステムであるため、回路は並んで存在します。したがって、さまざまな回路を接続するために必要なルーティングはごくわずかです。

- ASICには、タイミングの問題やポストプロダクション構成はありません。

ザ・ ASICの欠点 以下のものが含まれます。

- これらはカスタマイズされたチップであるため、プログラミングの柔軟性が低くなります。

- これらのチップはルートレベルから設計する必要があるため、ユニットあたりのコストが高くなります。

- ASICは、市場投入までの時間が長くなります。

ASICとFPGA

ASICとFPGAの違いは次のとおりです。

ASIC | FPGA |

| 再プログラム不可 | 再プログラム可能 |

| 大量生産に適しています | 少量生産に適しています |

| これらはアプリケーション固有です | システムのプロトタイプとして使用 |

| エネルギー効率が高いため、必要な電力が少なくて済みます | エネルギー効率が低いと、より多くの電力が必要になります |

| これらは永続的な回路であり、時々アップグレードすることはできません。 | 携帯電話チップ、基地局など、回路を時々アップグレードする必要があるアプリケーションに非常に適しています |

したがって、これはすべての概要についてです 特定用途向け集積回路 。 ASICの発明は、電子機器の使用方法に大きな変化をもたらしました。私たちはASICをさまざまなアプリケーションの形で日常生活の中で使用しています。 ASICのどのアプリケーションに出くわしましたか?どのタイプのASICを使用しましたか?