フライバック構成は、主に入力メインACからの出力DCの完全な分離を保証するため、SMPSアプリケーション設計で推奨されるトポロジです。その他の機能には、低い製造コスト、よりシンプルな設計、および複雑でない実装が含まれます。 50ワット未満の出力仕様を含むフライバックコンバータの低電流DCMバージョンは、大電流の対応するものよりも広く使用されています。

次の段落で包括的な説明を付けて詳細を学びましょう。

オフライン固定周波数DCMフライバックコンバータの包括的な設計ガイド

フライバック操作モード:DCMおよびCCM

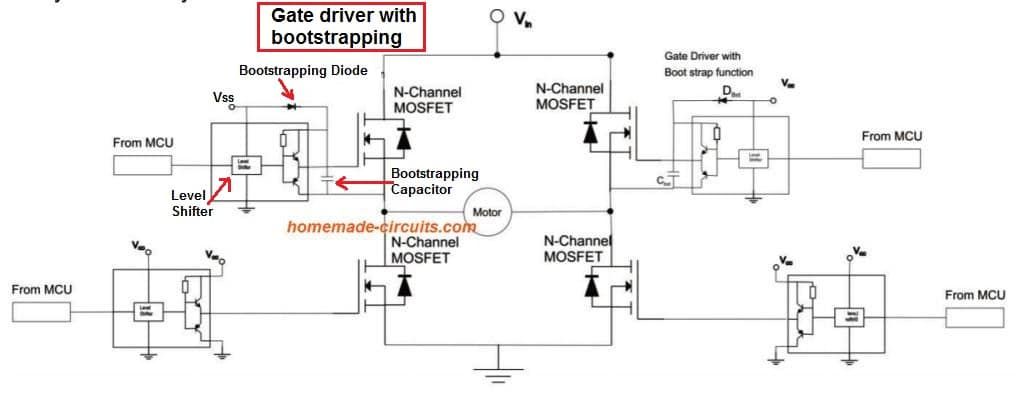

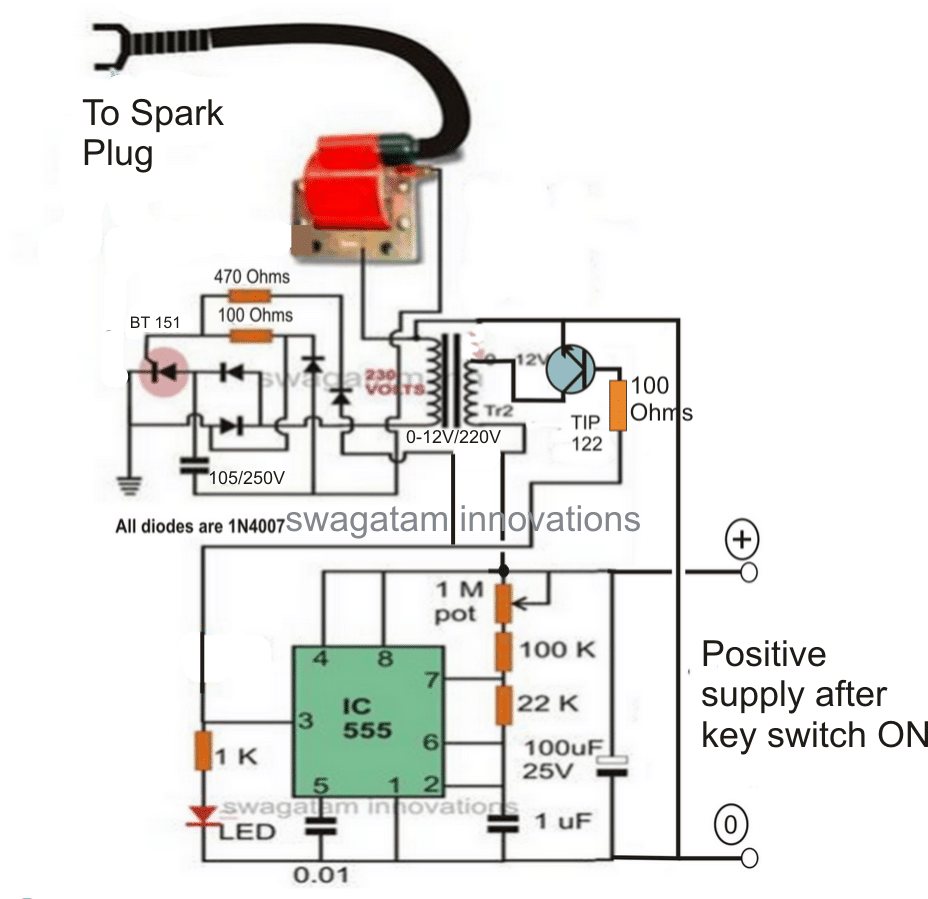

以下に、フライバックコンバータの基本的な回路図設計を示します。この設計の主なセクションは、変圧器、一次側のスイッチングパワーMOSFET Q1、二次側のブリッジ整流器D1、 平滑化用フィルターコンデンサ D1からの出力、およびIC制御回路である可能性のあるPWMコントローラーステージ。

このタイプのフライバック設計では、パワーMOSFET T1の構成方法に基づいて、CCM(連続導通モード)またはDCM(不連続導通モード)の動作が可能です。

基本的に、DCMモードでは、スイッチングサイクル(フライバック期間とも呼ばれます)中にMOSFETがオフになるたびに、トランスの一次側に蓄積された電気エネルギー全体が二次側に伝達され、一次側の電流がゼロ電位に達します。 T1が次のスイッチングサイクルで再びオンになる前。

CCMモードでは、一次側に蓄積された電気エネルギーは、二次側に完全に伝達または誘導される機会がありません。

これは、トランスが蓄積されたエネルギーをすべて負荷に転送する前に、PWMコントローラからの後続の各スイッチングパルスがT1をオンにするためです。これは、フライバック電流(ILPKおよびISEC)が各スイッチングサイクル中にゼロ電位に達することが決して許可されないことを意味します。

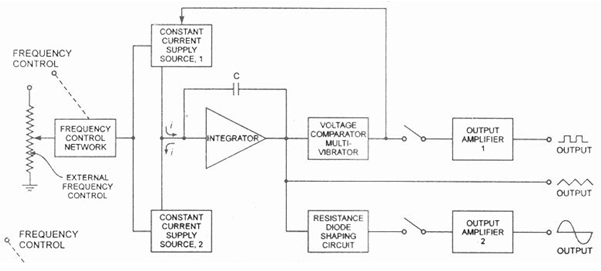

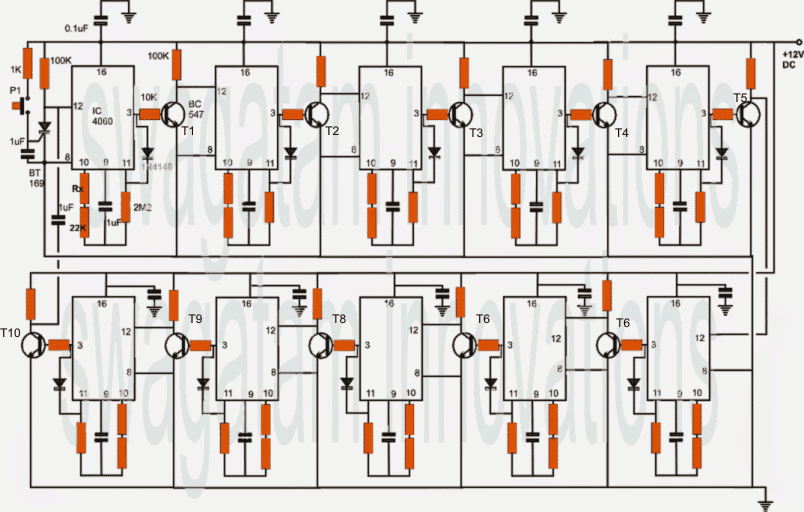

次の図では、変圧器の一次セクションと二次セクションの電流波形パターンを通じて、2つの動作モードの違いを確認できます。

DCMモードとCCMモードの両方に固有の利点があり、次の表から学ぶことができます。

CCMと比較して、DCMモード回路は、トランスの2次側で最適な電力を確保するために、より高いレベルのピーク電流を必要とします。これにより、一次側をより高いRMS電流で定格する必要があります。つまり、MOSFETを指定されたより高い範囲で定格する必要があります。

限られた範囲の入力電流とコンポーネントで設計を構築する必要がある場合は、通常、CCMモードのファイバックが選択されます。これにより、設計で比較的小さなフィルタコンデンサを使用でき、MOSFETとトランスの導通損失を低減できます。

CCMは、入力電圧が低く、電流が高い(6アンペアを超える)条件で有利になります。 50ワットの電力 ただし、ワット数仕様が50ワットより低くなる可能性がある5Vでの出力を除きます。

上の画像は、フライバックモードの一次側の電流応答と、それらの三角波形と台形波形の間の対応する関係を示しています。

三角波形のIAは、MOSFETのスイッチオン期間の開始時にゼロと見なされる可能性のある最小の初期化ポイントと、一次巻線で持続するより高い電流ピークレベルを示します。 変成器 CCM動作モード中、MOSFETが再びオンになるまでの時間。

IBは、現在の大きさの終点として認識される場合があります。 MOSFET スイッチがONになります(トン間隔)。

正規化された電流値IRMSは、Y軸上のK係数(IA / IB)の関数として見ることができます。

これは、平坦な上部波形を持つ台形波形を参照して、さまざまな数の波形に対して抵抗損失を計算する必要がある場合は常に、乗数として使用できます。

これは、電流波形関数として、トランス巻線とトランジスタまたはダイオードの非常に避けられないDC伝導損失も示しています。これらのアドバイスを利用することで、設計者は、このように適切に計算されたコンバータ設計で10〜15%の導通損失を防ぐことができます。

上記の基準を考慮することは、高RMS電流を処理するように設計されたアプリケーションにとって非常に重要になり、主要な機能として最適な効率を要求する可能性があります。

余分な銅損を排除することは可能かもしれませんが、それは手ごわいものを要求するかもしれません コアサイズ コア仕様のみが重要になる状況とは対照的に、本質的に大きな巻線ウィンドウ領域に対応するため。

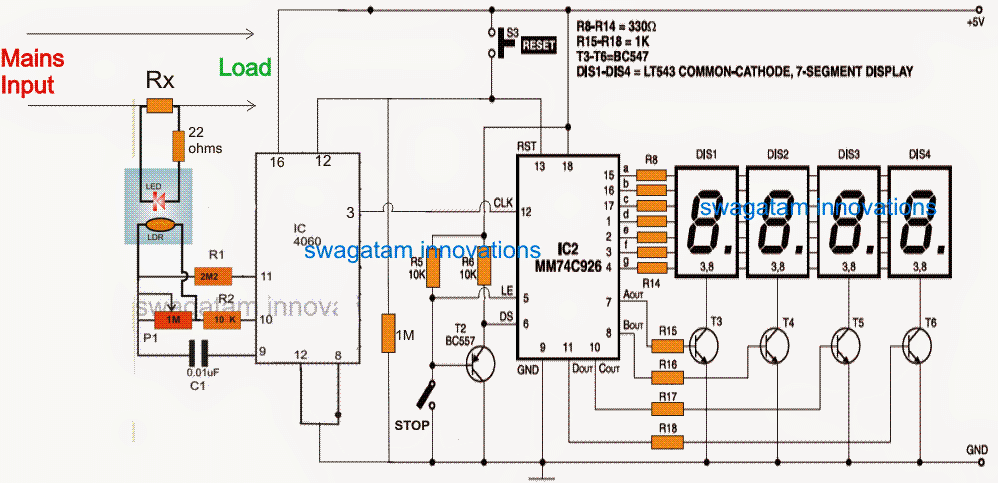

“時間遅延リレー回路図 ”

これまで理解してきたように、DCM動作モードでは、より小さなサイズのトランスを使用でき、より大きな過渡応答を備え、最小限のスイッチング損失で動作します。

したがって、このモードは、比較的低いアンペア要件でより高い出力電圧用に指定されたフライバック回路に強く推奨されます。

DCMモードとCCMモードで動作するフライバックコンバーターを設計することは可能かもしれませんが、DCMからCCMモードへの移行中に、このシフト機能が2極動作に変換され、低電圧が発生することを覚えておく必要があります。コンバータのインピーダンス。

この状況では、内部電流ループシステムに関するさまざまなループ(フィードバック)やスロープ補償など、追加の設計戦略を組み込むことが不可欠になります。実際には、これは、コンバーターが主にCCMモード用に設計されていることを確認する必要があることを意味しますが、出力でより軽い負荷が使用されている場合はDCMモードで動作できます。

高度な変圧器モデルを使用することにより、よりクリーンで軽い負荷調整、およびステップギャップ変圧器による広範囲の負荷にわたる高い相互調整によってCCMコンバーターを強化できる可能性があることを知ることは興味深いかもしれません。

このような場合、最初に高いインダクタンスを誘導し、より軽い負荷でCCM動作を可能にするために、絶縁テープや紙などの外部要素を挿入することによって小さなコアギャップが強制されます。これについては、次回の記事で詳しく説明します。

このような用途の広いDCMモード特性を備えているため、手間のかからない効率的で低電力のSMPSを設計する必要がある場合は、これが一般的な選択肢になります。

以下では、DCMモードフライバックコンバータの設計方法に関するステップバイステップの説明を学習します。

DCMフライバック設計方程式と順次決定要件

ステップ1:

設計要件を評価および見積もります。すべて SMPS設計 システム仕様を評価および決定することから始める必要があります。次のパラメータを定義して割り当てる必要があります。

効率パラメータは最初に決定する必要がある重要なパラメータであることがわかっています。最も簡単な方法は、設計が低コストの設計であっても、75%から80%程度の目標を設定することです。として示されるスイッチング周波数

Fswは通常、トランスのサイズとスイッチングによる損失、およびEMIを最大限に活用しながら、妥協する必要があります。これは、少なくとも150kHz未満のスイッチング周波数を決定する必要があるかもしれないことを意味します。通常、これは50kHzから100kHzの範囲で選択できます。

さらに、設計に複数の出力を含める必要がある場合は、最大電力値Poutを2つの出力の合計値として調整する必要があります。

最近まで、最も人気のある従来のSMPS設計にはMOSFETとが含まれていたことを知っておくと興味深いかもしれません。 PWMスイッチングコントローラー PCBレイアウト上で統合された2つの異なる分離ステージとして、しかし最近のSMPSユニットでは、これら2つのステージは1つのパッケージ内に埋め込まれ、単一のICとして製造されています。

主に、フライバックSMPSコンバーターの設計時に通常考慮されるパラメーターは、1)アプリケーションまたは負荷の仕様、2)コスト、3)待機電力、および4)追加の保護機能です。

組み込みICを使用すると、最適なフライバックコンバータを設計するためにトランスといくつかの外部受動部品を計算するだけで済むため、通常は非常に簡単になります。

フラバックSMPSを設計するための関連する計算に関する詳細を見てみましょう。

入力コンデンサのCinと入力DC電圧範囲の計算

入力電圧と電力の仕様に応じて、DCリンクコンデンサとも呼ばれるCinを選択するための標準的な規則は、次の説明から学ぶことができます。

幅広い動作を保証するために、DCリンクコンデンサに1ワットあたり2uF以上の値を選択できます。これにより、このコンポーネントの品質範囲を良好にすることができます。

次に、以下を解くことによって得られる最小DC入力電圧を決定する必要があるかもしれません。

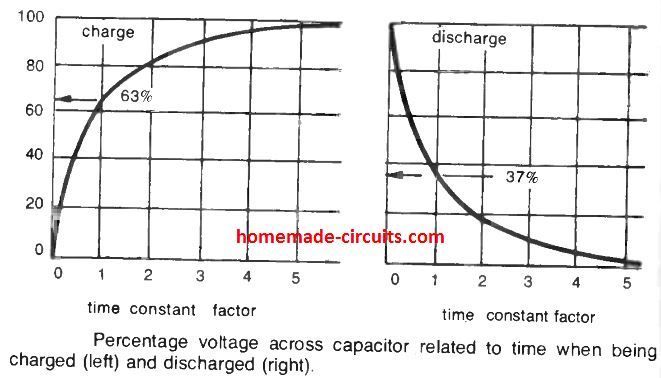

放電がDCリンクコンデンサのデューティ比になる場合、これは約0.2になる可能性があります

上の図では、DCリンクコンデンサの電圧を視覚化できます。示されているように、入力電圧は最大出力電力および最小入力AC電圧の間に発生しますが、最大DC入力電圧は最小入力電力(負荷がない場合)および最大入力AC電圧の間に発生します。

無負荷状態では、最大DC入力電圧を確認できます。この間、コンデンサはAC入力電圧のピークレベルで充電されます。これらの値は、次の式で表すことができます。

ステップ3:

フライバック誘導電圧VR、およびMOSFETVDSの最大電圧ストレスの評価。フライバック誘導電圧VRは、MOSFETQ1がスイッチオフ状態にあるときにトランスの一次側に誘導される電圧として理解できます。

上記の関数は、MOSFETの最大VDS定格に影響を与えます。これは、次の方程式を解くことによって確認および識別できます。

ここで、Vspikeは、トランスの漏れインダクタンスによって生成される電圧スパイクです。

まず、VDSmaxから30%のVspikeを取得できます。

次のリストは、定格650V〜800VのMOSFETに対して推奨される反射電圧または誘導電圧の量を示しており、予想される広大な入力電圧範囲に対して初期制限値VRが100V未満です。

適切なVRを選択することは、二次整流器の電圧ストレスのレベルと一次側MOSFETの仕様との間の交渉になる可能性があります。

巻数比を上げてVRを非常に高く選択すると、VDSmaxは大きくなりますが、2次側ダイオードの電圧ストレスのレベルは低くなります。

また、巻数比を小さくしてVRの選択が小さすぎると、VDSmaxは小さくなりますが、2次ダイオードのストレスレベルが増加します。

一次側VDSmaxを大きくすると、二次側ダイオードのストレスレベルが低くなり、一次電流が減少するだけでなく、費用効果の高い設計を実装できます。

DCMモードでのフライバック

VreflectedとVinminに応じてDmaxを計算する方法

VDCminのインスタンスでは、最大のデューティサイクルが期待できます。この状況では、DCMとCCMのしきい値に沿って変圧器を設計する場合があります。この場合、デューティサイクルは次のように表すことができます。

ステップ4:

一次インダクタンス電流の計算方法

このステップでは、一次インダクタンスと一次ピーク電流を計算します。

次の式を使用して、一次ピーク電流を特定できます。

上記が達成されたら、最大デューティサイクル境界内で、次の式を使用して一次インダクタンスを計算できます。

フライバックには注意が必要です。過剰な負荷条件が原因でCCMモードにならないようにする必要があります。このため、式#5でPoutmaxを計算する際には、この最大電力仕様を考慮する必要があります。上記の状態は、インダクタンスがLprimax値を超えて増加した場合にも発生する可能性があるため、これらに注意してください。

ステップ5 :

最適なコアグレードとサイズを選択する方法:

フライバックを初めて設計する場合は、適切なコア仕様と構造を選択する際に非常に威圧的に見えるかもしれません。これには、考慮すべきかなりの数の要因と変数が含まれる可能性があるためです。重要な可能性のあるこれらのいくつかは、コアの形状(EEコア/ RMコア/ PQコアなど)、コアの寸法(EE19、RM8 PQ20など)、およびコアの材料(3C96、TP4、3F3など)です。等)。

上記の仕様をどのように進めるかがわからない場合、この問題に対処する効果的な方法は、 標準コア選択ガイド コアの製造元によって、または次の表を参考にして、出力電力を参照して65kHzDCMフライバックを設計する際の標準コア寸法を大まかに示します。

コアサイズの選択が完了したら、コアデータシートに従って取得できる正しいボビンを選択します。ピン数、PCBマウントまたはSMD、水平または垂直位置決めなどのボビンの追加のプロパティも、推奨される設計として考慮する必要があります。

コア材料も重要であり、周波数、磁束密度、およびコア損失に基づいて選択する必要があります。

まず、3F3、3C96、またはTP4Aという名前のバリアントを試すことができます。使用可能なコア材料の名前は、特定の製造元によって同じタイプで異なる場合があることに注意してください。

最小一次巻数または巻線を計算する方法

用語がどこに Bmax は動作最大磁束密度を示し、Lpriは一次インダクタンスについて示し、Ipriは一次ピーク電流になり、Aeは選択したコアタイプの断面積を示します。

Bmaxは、コア材料のデータシートで指定されている飽和磁束密度(Bsat)を超えてはならないことを覚えておく必要があります。材料の種類や温度などの仕様によっては、フェライトコアのBsatにわずかな違いが見られる場合がありますが、これらの大部分は400mTに近い値になります。

詳細な参照データが見つからない場合は、Bmaxを300mTにすることができます。より高いBmaxを選択すると、一次巻数を減らして導通を下げるのに役立つ場合がありますが、コア損失が大幅に増加する可能性があります。コア損失と銅損の両方が許容範囲内に保たれるように、これらのパラメータの値の間で最適化するようにしてください。

ステップ6:

主二次出力(Ns)とその他の補助出力(Naux)の巻数の計算方法

のために 二次ターンを決定する まず、次の式を使用して計算できる巻数比(n)を見つける必要があります。

ここで、Npは一次巻数、Nsは二次巻数です。Voutは出力電圧を示し、VDは二次ダイオードの両端の電圧降下を示します。

目的のVcc値の補助出力の巻数を計算するには、次の式を使用できます。

補助巻線は、制御ICに初期起動電源を供給するためにすべてのフライバックコンバータで重要になります。この電源VCCは通常、一次側のスイッチングICに電力を供給するために使用され、ICのデータシートに記載されている値に従って固定できます。計算で非整数値が得られた場合は、この非整数のすぐ上にある上位整数値を使用して、単純に丸めます。

選択した出力巻線のワイヤサイズを計算する方法

複数の巻線のワイヤサイズを正しく計算するには、最初に個々の巻線のRMS電流仕様を見つける必要があります。

これは、次の式で実行できます。

出発点として、アンペアあたり150〜400サーキュラーミルの電流密度を使用して、ワイヤのゲージを決定できます。次の表は、RMS電流値に従って、200M / Aを使用して適切なワイヤゲージを選択するためのリファレンスを示しています。また、ワイヤーの直径と、スーパーエナメル銅線のさまざまなゲージの基本的な絶縁も示しています。

ステップ8:

トランスの構造と巻線設計の反復を考慮

上記のトランスパラメータの決定が完了したら、計算されたトランスコアサイズと指定されたボビン内にワイヤの寸法と巻数をどのように適合させるかを評価することが重要になります。これを最適に行うには、ワイヤゲージと巻数を参照してコア仕様を最適化するために、数回の反復または実験が必要になる場合があります。

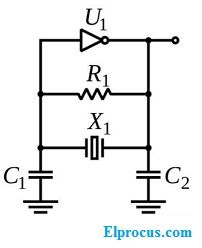

次の図は、特定の巻線領域を示しています EEコア 。計算された線の太さと個々の巻線の巻数を参照すると、巻線が使用可能な巻線領域(wおよびh)に適合するかどうかを概算できる場合があります。巻線が対応しない場合は、巻数、ワイヤゲージ、コアサイズのいずれかのパラメータ、または複数のパラメータで、巻線が最適に適合するまで微調整が必要になる場合があります。

巻線のレイアウトは、作業性能とトランスの信頼性がそれに大きく依存するため、非常に重要です。図5に示すように、インダクタンスの漏れを制限するために、巻線にサンドイッチレイアウトまたは構造を採用することをお勧めします。

また、国際安全規則を満たし、準拠するために、設計には、巻線の一次層と二次層にわたって十分な範囲の絶縁が必要です。これは、次のそれぞれの図に示すように、マージン巻線構造を採用するか、三重絶縁ワイヤ定格の2次ワイヤを使用することで保証できます。

二次巻線に三重絶縁電線を採用することは、フライバックSMPS設計に関する国際安全法を迅速に確認するためのより簡単なオプションになります。しかしながら、そのような強化されたワイヤーは、巻線がより多くのスペースを占めることを強いる通常の変形と比較して少し厚いかもしれず、選択されたボビン内に収容するために追加の努力を必要とするかもしれない。

ステップ9

一次クランプ回路の設計方法

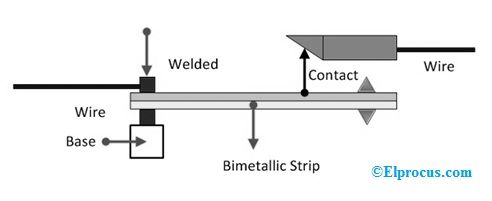

スイッチングシーケンスでは、MOSFETのオフ期間中に、漏れインダクタンスの形で高電圧スパイクがMOSFETのドレイン/ソース全体にかかり、アバランシェ降伏を引き起こし、最終的にMOSFETに損傷を与える可能性があります。

これに対抗するために、クランプ回路は通常、一次巻線の両端に構成され、生成されたスパイクを安全な低い値に即座に制限します。

次の図に示すように、この目的のために組み込むことができるいくつかのクランプ回路設計があります。

つまり、RCDクランプとダイオード/ツェナークランプであり、後者は最初のオプションよりも構成と実装がはるかに簡単です。このクランプ回路では、サージスパイクをクランプするために、整流ダイオードとTVS(過渡電圧サプレッサー)などの高電圧ツェナーダイオードの組み合わせを使用します。

の機能 ツェナーダイオード 漏れ電圧がツェナーダイオードを介して完全にシャントされるまで、電圧スパイクを効率的にクリップまたは制限することです。ダイオードツェナークランプの利点は、VRとVspikeの合計値がツェナーダイオードのブレークダウン仕様を超えた場合にのみ回路がアクティブ化およびクランプされることです。逆に、スパイクがツェナーブレークダウンまたは安全レベルを下回っている限り、クランプがまったくトリガーされない場合があり、不要な電力損失が発生しません。

クランプダイオード/ツェナー定格の選択方法

常に反射電圧VRの値または想定スパイク電圧の2倍である必要があります。

整流ダイオードは、超高速回復または最大DCリンク電圧よりも高い定格のショットキータイプのダイオードである必要があります。

RCDタイプのクランプの代替オプションには、MOSFETのdv / dtが遅くなるという欠点があります。ここでは、電圧スパイクを制限しながら、抵抗の抵抗パラメータが重要になります。低い値のRclampを選択すると、スパイク保護は向上しますが、消費電力と無駄なエネルギーが増加する可能性があります。逆に、より高い値のRclampが選択された場合、それは散逸を最小限に抑えるのに役立ちますが、 スパイクの抑制 。

上の図を参照すると、VR = Vspikeを確実にするために、次の式を使用できます。

Lleakはトランスのインダクタンスを意味し、2次巻線の両端を短絡することで見つけることができます。あるいは、1次インダクタンス値の2〜4%を適用することで、経験則を組み込むことができます。

この場合、コンデンサのクランプは実質的に大きく、漏れエネルギーの吸収期間中の電圧の上昇を抑制します。

Cclampの値は100pFから4.7nFの間で選択でき、このコンデンサー内に蓄積されたエネルギーは、eacjスイッチングサイクル中にRclampによって迅速に放電およびリフレッシュされます。

ステップ10

出力整流ダイオードの選び方

これは、上記の式を使用して計算できます。

ダイオードの最大逆電圧またはVRRMがVRVdiodeより30%以上になるように仕様を選択し、IFまたはアバランシェ順電流仕様がIsecRMSよりも50%以上大きくなるようにしてください。伝導損失を最小限に抑えるために、ショットキーダイオードを使用することをお勧めします。

DCM回路では、フライバックのピーク電流が高くなる可能性があるため、目的の効率レベルに関して、順方向電圧が低く、電流仕様が比較的高いダイオードを選択してみてください。

ステップ11

出力コンデンサ値の選択方法

を選択する 正しく計算された出力コンデンサ フライバックの設計では、ダイオードとコンデンサの間で蓄積された誘導エネルギーが利用できないため、非常に重要になる可能性があります。これは、コンデンサの値を3つの重要な基準を考慮して計算する必要があることを意味します。

1)静電容量

2)ESR

3)RMS電流

可能な最小値は、最大許容ピークツーピーク出力リップル電圧の関数に応じて特定でき、次の式で特定できます。

ここで、Ncpは、指定された最大値と最小値からデューティを制御するために制御フィードバックに必要な一次側クロックパルスの数を示します。これには通常、約10〜20回のスイッチングサイクルが必要です。

Ioutは、最大出力電流を指します(Iout = Poutmax / Vout)。

出力コンデンサの最大RMS値を特定するには、次の式を使用します。

フライバックの指定された高いスイッチング周波数の場合、トランスの2次側からの最大ピーク電流は、出力コンデンサの等価ESRの両端に課せられる、対応する高いリップル電圧を生成します。これを考慮して、コンデンサのESRmax定格がコンデンサの指定された許容リップル電流能力を超えないようにする必要があります。

最終的な設計には、基本的に、選択した出力電圧とフライバックの電流の実際の比率に基づいて、コンデンサの望ましい電圧定格とリップル電流能力を含めることができます。

を確認してください ESR値 は、1kHzより高い周波数に基づいてデータシートから決定されます。これは通常、10kHzから100kHzの間であると想定されます。

出力リップルを制御するには、ESR仕様が低い単独のコンデンサで十分な場合があることに注意してください。特にフライバックがDCMモードで動作するように設計されている場合は、より高いピーク電流用に小さなLCフィルタを含めることができます。これにより、出力でのリップル電圧制御が適度に良好になる可能性があります。

ステップ12

さらに重要な考慮事項:

A)一次側ブリッジ整流器の電圧および電流定格の選択方法。

上記の式で行うことができます。

この式では PFは力率の略です 電源の適切な基準が届かなくなった場合に備えて、0.5を適用できます。ブリッジ整流器には、IACRMSの2倍の順方向アンペア定格を持つダイオードまたはモジュールを選択します。定格電圧については、最大400VAC入力仕様の600Vで選択できます。

B)電流センス抵抗(Rsense)の選択方法:

次の式で計算できます。検出抵抗Rsenseは、フライバックの出力での最大電力を解釈するために組み込まれています。 Vcsth値は、コントローラーICデータシートを参照して決定できます。Ip(max)は一次電流を示します。

C)コンデンサのVCCの選択:

最適 静電容量値 入力コンデンサが適切な起動期間を提供するために重要です。通常、22uFから47uFの間の任意の値がうまく機能します。ただし、これをはるかに低く選択すると、コンバータがVccを発生させる前に、コントローラICで「低電圧ロックアウト」がトリガーされる可能性があります。逆に、容量値が大きいと、コンバータの起動時間が望ましくない遅延を引き起こす可能性があります。

さらに、このコンデンサが最高品質であり、出力と同等の非常に優れたESRおよびリップル電流仕様を備えていることを確認してください コンデンサの仕様 。 100nFのオーダーで、上記のコンデンサと並列に、コントローラICのVcc /グランドピン配列にできるだけ近い別の小さい値のコンデンサを接続することを強くお勧めします。

D)フィードバックループの構成:

フィードバックループ補償は、発振の発生を停止するために重要になります。電力段に「右半平面ゼロ」がないため、DCMモードのフライバックのループ補償の構成はCCMよりも簡単であり、補償は必要ありません。

上の図に示されているように、単純なRC(Rcomp、Ccomp)は、ほとんどの場合、ループ全体で良好な安定性を維持するのに十分になります。一般に、Rcomp値は1Kから20Kの間で選択できますが、Ccompは100nFから470pFの範囲内にあります。

これで、フライバックコンバーターの設計と計算方法に関する詳細な説明は終わりです。提案や質問がある場合は、次のコメントボックスに入力してください。質問には、できるだけ早く回答します。

礼儀: インフィニオン

前:超音波ワイヤレス水位インジケーター–ソーラーパワー 次へ:PIDコントローラーについて