私たちは皆、バック回路とブースト回路について多くのことを聞いており、基本的にこれらの回路は、入力の特定の電圧をステップアップまたはステップダウンするためにSMPS設計で使用されることを知っています。この技術の興味深い点は、上記の機能を無視できるほどの発熱で可能にし、非常に効率的な変換を実現することです。

Buck-Boostとは何ですか、どのように機能しますか

初心者でも正確にバックブーストの概念が何であるかを理解しやすくするために、多くの技術を必要とせずに最初のセクションで概念を学びましょう。

buck、boost、buck-boostという3つの基本的なトポロジーの中で、3番目のトポロジーは、入力パルスを変更するだけで両方の機能(buck boost)を単一の構成で使用できるため、より一般的です。

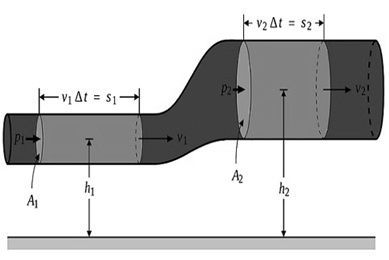

昇降圧トポロジーでは、主にトランジスタまたはMOSFETの形をとることができる電子交換コンポーネントがあります。このコンポーネントは、集積発振回路からの脈動信号を介して切り替えられます。

上記のスイッチング部品とは別に、回路にはインダクタ、ダイオード、コンデンサが主成分です。

これらのパーツはすべて、次の図に示されている形式で配置されています。

上記の降圧ブースト図を参照すると、MOSFETは、オン状態とオフ状態の2つの条件で動作するように強制するパルスを受信する部分です。

オン状態の間、入力電流はMOSFETを通る明確な経路を取得し、ダイオードが逆バイアス状態に配置されているため、即座にインダクタを通過しようとします。

インダクタは、その固有の特性により、突然の電流の流入を制限しようとし、補償応答で、ある量の電流をインダクタに蓄積します。

これで、MOSFETがオフになるとすぐにオフ状態になり、入力電流の通過がブロックされます。

この場合も、インダクタはこの電流の所定の大きさからゼロへの突然の変化に対処できず、これを補償するために、回路の出力の両端でダイオードを介して蓄積された電流をキックバックします。

その過程で、電流もコンデンサに蓄積されます。

MOSFETの次のオン状態の間、サイクルは上記のように繰り返されますが、インダクタから利用可能な電流がない場合、コンデンサは蓄積されたエネルギーを出力に放電し、出力を最適化された程度に安定に保つのに役立ちます。

出力でのBUCKまたはBOOSTの結果を決定する要因は何か疑問に思われるかもしれません。これは非常に簡単です。MOSFETがオン状態またはオフ状態にとどまることができる時間によって異なります。

MOSFETのオン時間が長くなると、回路はブーストコンバータに変換され始めますが、MOSFETのオフ時間がオン時間を超えると、回路はバックコンバータのように動作します。

したがって、MOSFETへの入力は、同じ回路で必要な遷移を取得するために最適化されたPWM回路を介して行うことができます。

SMPS回路のバック/ブーストトポロジをより技術的に調査する:

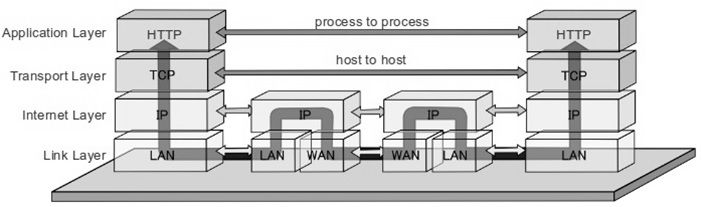

上記のセクションで説明したように、スイッチモード電源で一般的に使用される3つの基本的なトポロジは、降圧、昇圧、および降圧ブーストです。

これらは基本的に非絶縁であり、入力電力段は出力電力セクションと共通ベースを共有します。もちろん、非常にまれですが、分離されたバージョンを見つけることもできます。

上記の3つのトポロジーは、それらの排他的な特性に応じて一意に区別できます。特性は、定常状態の電圧変換比、入力電流と出力電流の性質、および出力電圧リップルの特性としても識別できます。

さらに、出力電圧の実行に対するデューティサイクルの周波数応答は、重要な特性の1つと見なすことができます。

上記の3つのトポロジの中で、バックブーストトポロジが最も好ましいトポロジです。これは、出力が入力電圧よりも低い電圧で動作し(バックモード)、入力電圧よりも高い電圧を生成できるためです(ブーストモード)。

ただし、出力電圧は常に入力とは逆の極性で取得できるため、問題は発生しません。

バックブーストコンバータに印加される入力電流は、関連する電源スイッチ(Q1)のスイッチングによる脈動電流の形です。

ここでは、電流はパルスサイクルごとにゼロからlに切り替わります。出力にも同じことが当てはまり、関連するダイオードが一方向にのみ導通するために脈動電流が発生し、スイッチングサイクル中にオンとオフの脈動状態が発生します。 。

コンデンサは、スイッチングサイクル中にダイオードがスイッチオフまたは逆バイアス状態にあるときに補償電流を供給する役割を果たします。

この記事では、連続モードおよび不連続モード動作での昇降圧コンバータの定常状態機能について、例示的な波形を使用して説明します。

デューティサイクルから出力への電圧交換機能は、PWMスイッチ設計の導入後に提示されます。

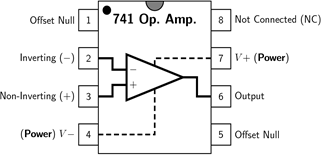

図1は、駆動回路ブロックが追加された昇降圧パワー段の単純な回路図です。電源スイッチQ1はnチャネルMOSFETです。出力ダイオードはCR1です。

インダクタLとコンデンサCは、効率的な出力フィルタリングを構成します。コンデンサのESR、RC(等価直列抵抗)とインダクタのDC抵抗、RLは、すべてで分析されます。抵抗Rは、パワーステージ出力によって識別される負荷に対応します。

昇降圧パワー段の通常の機能の過程で、Q1は常にオンとオフになり、オン時間とオフ時間は制御回路によって制御されます。

このスイッチング動作により、Q1、CR1、およびLの接合部で一連のパルスが可能になります。

インダクタLが出力コンデンサCにリンクされていても、CR1のみが導通すると、L / C出力フィルタが正常に確立されます。一連のパルスをクリーニングして、DC出力電圧を生成します。

昇降圧ステージの定常状態解析

パワーステージは、連続または不連続のインダクタ電流設定で機能する場合があります。連続インダクタ電流モードは、定常状態プロセスのスイッチングシーケンスにわたってインダクタに連続的に流れる電流によって識別されます。

不連続インダクタ電流モードは、スイッチングサイクルのセクションでインダクタ電流がゼロのままであることによって識別されます。ゼロから始まり、最大値まで伸び、すべてのスイッチングパターンの過程でゼロに戻ります。

その後、2つの異なる方法についてさらに詳しく説明し、定格負荷の能力として選択された機能モードを維持するためのインダクタ値のモデル提案を示します。パワーステージの周波数応答は2つの異なる動作技術間で大幅に変化するため、コンバータが予測される機能状況でのみ単一の形式であることがかなり有利です。

この評価では、nチャネルパワーMOSFETが採用され、正の電圧VGS(ON)が制御回路によってゲートからQ1のソース端子に供給され、FETがオンになります。 nチャネルFETを採用する利点は、RDS(on)が低いことですが、サスペンドドライブが必要になるため、制御回路には注意が必要です。同一のパッケージ寸法の場合、pチャネルFETはより高いRDS(on)を備えていますが、通常、フローティングドライブ回路は必要ありません。

トランジスタQ1とダイオードCR1は、a、p、cのタグが付いた端子が付いた破線の輪郭の内側に示されています。これについては、昇降圧パワーステージモデリングの部分で詳しく説明します。

昇降圧定常状態連続伝導モード解析

以下は、連続導通方式の定常運転で動作する降圧ブーストの説明です。このセグメントの主な目的は、連続導通モードの昇降圧電力段の電圧変換関係の導出を提示することです。

これは、出力電圧がデューティサイクルと入力電圧によって決定される方法、または逆に、入力電圧と出力電圧に応じてデューティサイクルが決定される方法を示すため、重要になります。

定常状態とは、入力電圧、出力電圧、出力負荷電流、およびデューティサイクルが変化するのではなく一定であることを意味します。大文字は通常、定常状態の大きさを示すために変数ラベルに提供されます。連続導通モードでは、昇降圧コンバータはスイッチングサイクルごとにいくつかの状態を取ります。

オン状態は、Q1がオンでCR1がオフになるたびです。オフ状態は、Q1がオフでCR1がオンになるたびです。簡単な線形回路は、回路内のスイッチが各状態の過程でそれらのマッチング回路によって置き換えられる2つの状態のそれぞれを象徴することができます。 2つの条件のそれぞれの回路図を図2に示します。

オン状態の周期はD×TS = TONであり、ここでDはデューティサイクルであり、駆動回路によって固定され、単一の完全なスイッチングシーケンスの周期Tsに対するスイッチのオン周期の比率の形式で表されます。

オフ状態の長さはTOFFとして知られています。連続導通モードの場合、スイッチングサイクルごとに2、3の条件を見つけることができるため、TOFFは(1-D)×TSに等しくなります。マグニチュード(1-D)はD ’と呼ばれることもあります。これらの周期は、図3の波形とともに示されています。

図2を見ると、ON状態の過程で、Q1はドレインからソースまでの抵抗RDS(on)が減少し、VDS = IL×RDS(on)の電圧降下が小さくなります。

さらに、インダクタのDC抵抗の両端にIL×RLに等しいわずかな電圧降下があります。

これにより、入力電圧VIから赤字を差し引いた値(VDS + IL×RL)がインダクタLの両端に印加されます。CR1は逆バイアスされるため、この期間内にオフになります。

インダクタ電流ILは、入力電源VIからQ1を経由してグランドに流れます。 ON状態の間、インダクタの両端にかかる電圧は一定であり、VI − VDS −IL×RLと同じです。

図2に示されている電流ILの極性基準に従って、実行電圧によってインダクタ電流がブーストされます。さらに、印加電圧は基本的に一定であるため、インダクタ電流は直線的に上昇します。 TONの過程でのインダクタ電流のこのブーストは、図3に示されています。

インダクタ電流がブーストするレベルは、一般に、よく知られている式の形式を利用して決定されます。

オン状態の過程でのインダクタ電流の上昇は、次のように表されます。

この大きさΔIL(+)は、インダクタリップル電流と呼ばれます。さらに、この間隔を通じて、出力負荷電流のすべてのビットが出力コンデンサCから入ることに注意してください。

図2を参照すると、Q1がオフの間、ドレインからソースへのインピーダンスが増加します。

その結果、インダクタLを流れる電流は瞬時に調整できないため、電流はQ1からCR1に切り替わります。インダクタ電流が減少した結果、整流器CR1が順方向にバイアスされてオンになるまで、インダクタ両端の電圧の極性が反転します。

Lの両端に接続された電圧は、(VO − Vd − IL×RL)に変わります。ここで、大きさVdはCR1の順方向電圧降下です。この時点でのインダクタ電流ILは、出力コンデンサと負荷抵抗の配置からCR1を経由して負のラインに流れます。

CR1とインダクタ内の電流循環の経路の整合は、出力コンデンサと負荷抵抗のグループ化で流れる電流がVOをマイナス電圧にすることを意味することに注意してください。オフ状態の間、インダクタの両端に接続されている電圧は安定しており、(VO − Vd − IL×RL)と同じです。

同様の極性の規則を維持すると、出力電圧VOが負であるため、この接続電圧はマイナスになります(またはオン時間中に接続電圧と極性が逆になります)。

“赤外線懐中電灯の作り方 ”

したがって、インダクタ電流はオフ時間を通して低下します。さらに、接続電圧は基本的に安定しているため、インダクタ電流は直線的に減少します。 TOFFの過程でのインダクタ電流のこの減少は、図3に概説されています。

オフ状態によるインダクタ電流の減少は、次の方法で提供されます。

この大きさΔIL(-)は、インダクタのリップル電流と呼ぶことができます。安定状態の状況では、オン時間中の電流上昇ΔIL(+)とオフ時間中の電流減少ΔIL(-)は同じでなければなりません。

さもなければ、インダクタ電流は、安定した状態の状況ではないであろうサイクルからサイクルへの全体的なブーストまたはリダクションを提供する可能性があります。

したがって、これらの方程式の両方を同等にして、VOがバックブースト電圧切り替えアフィリエーションから連続伝導を取得するように計算することができます。

VOの決定:

また、TON + TOFFの代わりにTSを使用し、D = TON / TSおよび(1-D)= TOFF / TSを使用すると、VOの定常状態の式は次のようになります。

上記を単純化する際に、TON + TOFFはTSに類似していると想定されていることに注意してください。これは、不連続伝導モードの評価で発見するように、連続伝導モードに対してのみ本物である可能性があります。この時点で、本質的な精査を行う必要があります。

ΔILの2つの値を互いに同等に固定することは、インダクタのボルト秒を平準化することとまったく同じです。インダクタで使用されるボルト秒は、使用される電圧と電圧が印加される期間の積です。

これは、一般的な回路パラメータに関して、たとえばVOやDなどの未確認の大きさを推定するための最も効果的な方法であり、このアプローチはこの記事内で頻繁に使用されます。インダクタのボルト秒安定化は自然な要件であり、少なくとも追加的にオームの法則として認識されるべきです。

上記のΔIL(+)およびΔIL(-)の式では、出力電圧は、オン時間およびオフ期間全体にわたってACリップル電圧がなくても一貫していると暗黙的に想定されていました。

これは受け入れられている単純化であり、いくつかの個別の結果を伴います。第一に、出力コンデンサは、その電圧変換が最小であるように十分に大きいと考えられています。

第二に、コンデンサESRの電圧はさらに最小と見なされます。 ACリップル電圧は出力電圧のDC部分よりも確実に大幅に低くなるため、このような仮定は正当です。

上記のVOの電圧変化は、デューティサイクルDを微調整することでVOを微調整できるという事実を示しています。

この接続は、Dがゼロに近づくとゼロに近づき、Dが1に近づくと運命づけられずに上昇します。一般的な単純化では、VDS、Vd、およびRLは無視できるほど小さいと考えられます。 VDS、Vd、およびRLをゼロに設定すると、上記の式は次のように著しく単純化されます。

回路動作を描写するためのそれほど複雑ではない定性的な方法は、インダクタを電力貯蔵部品として考えることです。 Q1がオンになるたびに、エネルギーがインダクターに注がれます。

Q1がオフの間、インダクタはそのエネルギーの一部を出力コンデンサと負荷に戻します。出力電圧は、Q1のオン時間を確立することによって調整されます。たとえば、Q1のオン時間を上げると、インダクタに送られる電力量が増幅されます。

その後、Q1のオフ時間の過程で追加のエネルギーが出力に送られ、出力電圧が上昇します。降圧電力段とは対照的に、インダクタ電流の一般的な大きさは出力電流と同じではありません。

インダクタ電流を出力電流に関連付けるには、図2と図3を見て、パワーステージがオフの状態にあるときだけ、出力へのインダクタ電流を観察します。

出力コンデンサの近似電流はゼロに等しいはずなので、スイッチングシーケンス全体で平均化されたこの電流は出力電流と同じです。

連続モード昇降圧パワー段の平均インダクタ電流と出力電流の間の接続は、次の方法で提供されます。

もう1つの重要な視点は、典型的なインダクタ電流が出力電流に比例するという事実です。インダクタリップル電流ΔILは出力負荷電流とは無関係であるため、インダクタ電流の最小値と最大値は平均インダクタ電流に正確に従います。

例として、負荷電流の減少により平均インダクタ電流が2A減少した場合、インダクタ電流の最小値と最大値は2A減少します(連続導通モードが維持されることを考慮)。

前述の評価は、連続インダクタ電流モードでの昇降圧パワー段機能に関するものでした。次のセグメントは、不連続伝導モードでの定常状態機能の説明です。主な結果は、不連続導通モードの昇降圧電力段の電圧変換関係の導出です。

昇降圧定常状態の不連続伝導モードの評価

この時点で、負荷電流が減少し、導通モードが連続から不連続に移行した場合に何が発生するかを調べます。

連続導通モードの場合、平均インダクタ電流は出力電流よりも遅くなります。つまり、出力電流が減少した場合、平均インダクタ電流も減少します。

さらに、インダクタ電流の最低ピークと最高ピークは、平均インダクタ電流を正確に追跡します。出力負荷電流が基本電流レベルを下回った場合、スイッチングシーケンスの一部でインダクタ電流はゼロになります。

これは、リップル電流のピークツーピークレベルが出力負荷電流によって変化することができないため、図3に示されている波形から明らかです。

昇降圧電力段では、インダクタ電流がゼロを下回ろうとすると、(CR1での一方向電流が移動するため)ゼロで停止し、後続のスイッチング動作が始まるまでそこに留まります。この動作モードは、不連続伝導モードとして知られています。

不連続導通フォーマットの降圧ブースト回路のパワーステージ動作は、連続導通フォーマットの2つの状態とは対照的に、すべてのスイッチングサイクルを通じて3つの特徴的な状態を持っています。

パワーステージが連続設定と不連続設定の間の周辺にあるインダクタ電流状態を図4に示します。

この場合、インダクタ電流は単純にゼロに崩壊し、電流がゼロに達した直後に次のスイッチングサイクルが始まります。 IOとILには反対の極性が含まれているため、IOとIO(Crit)の値が図4に示されていることに注意してください。

出力負荷電流をさらに下げると、パワーステージが不連続な導通パターンになります。この状態を図5に示します。

不連続モードのパワーステージ周波数応答は、バックブーストパワーステージモデリングセグメントで示されている連続モード周波数応答とはかなり異なります。さらに、このページの派生で示されているように、入力から出力への接続はかなり多様です。

不連続導通モードの昇降圧電力段の電圧切り替え比の導出を開始するには、コンバータが不連続導通モード機能を通じて考慮する3つの特徴的な状態があることを思い出してください。

ON状態は、Q1がONでCR1がOFFのときです。 OFF状態は、Q1がOFFでCR1がONのときです。 IDLE状態は、各Q1とCR1がオフのときです。最初の2つの条件は、連続モードの状況と非常によく似ており、図2の回路は、TOFF≠(1-D)×TSを除いて関連しています。残りのスイッチングシーケンスはIDLE状態です。

さらに、出力インダクタのDC抵抗、出力ダイオードの順方向電圧降下、およびパワーMOSFETのオン状態の電圧降下は、通常、見落とすのに十分なほど小さいと考えられています。

オン状態の期間はTON = D×TSです。ここで、Dはデューティサイクルであり、制御回路によって固定され、1つの完全なスイッチングシーケンスの時間に対するターンオン時間の比率Tsとして示されます。オフ状態の長さはTOFF = D2×TSです。 IDLE期間は、TS − TON − TOFF = D3×TSとして表される残りのスイッチングパターンです。これらの期間は、図6の波形に対応しています。

包括的な説明を確認せずに、インダクタ電流の上昇と下降の式を以下に列挙します。オン状態の過程でのインダクタ電流の上昇は、次の原因で発生します。

リップル電流量ΔIL(+)は、同様にピークインダクタ電流Ipkです。これは、不連続モードでは、電流がサイクルごとに0から始まるためです。オフ状態の過程でのインダクタ電流の減少は、次の式で表されます。

連続導通モードの状況と同様に、オン時間中の電流上昇ΔIL(+)とオフ時間中の電流減少ΔIL(-)は同じです。したがって、これらの方程式の両方は、電圧変換比を解くために利用される2つの方程式のイニシャルを取得するために、VOに対して同等化および対処できます。

次に、出力電流(出力電圧VOを出力負荷Rで割った値)を決定します。これは、CR1が導通したときのインダクタ電流の1つのスイッチングシーケンスの平均です(D2×TS)。

ここで、IPKの接続(ΔIL(+))を上記の式に置き換えて、次の式を取得します。

したがって、2つの方程式があります。1つは導出したばかりの出力電流(VOをRで割ったもの)の方程式で、もう1つは出力電圧の方程式です。どちらもVI、D、およびD2に関するものです。この時点で、D2の各式を解き、2つの方程式を互いに同等に修正します。

得られた式を利用して、出力電圧VOの図を入手することができます。不連続導通モードの昇降圧電圧変換の所属は、次のように記述されます。

上記の接続は、2つの伝導モード間の主な相違点の1つを示しています。不連続導通モードの場合、電圧変化の関係は、入力電圧、デューティサイクル、パワーステージのインダクタンス、スイッチング周波数、および出力負荷抵抗の関数です。

連続導通モードの場合、電圧切り替え接続は入力電圧とデューティサイクルの影響を受けるだけです。従来のアプリケーションでは、昇降圧パワー段は連続導通モードまたは不連続導通モードのいずれかを選択して実行されます。特定の使用法では、同じモードを維持するために電力段が作成されている間に、1つの導通モードが選択されます。

前:PICチュートリアル-レジスタから割り込みまで 次へ:IC555自動非常灯回路