2進数から10進数への変換は、デバイス、つまりデコーダーを使用して実行できます。このデバイスは、n入力ラインを使用して2n出力ラインを生成する一種の組み合わせ論理回路です。ここで、このデバイスの出力は2n行未満になる可能性があります。複数の入力と複数の出力を含むさまざまな種類のバイナリデコーダがあります。一部の種類のデコーダには、データ入力とともに1つ以上のイネーブル入力が含まれています。イネーブル入力が無効になると、すべての出力が非アクティブになります。その機能に基づいて、バイナリデコーダはデータをn入力信号から2n出力信号に変更します。一部の種類のデコーダーでは、2n未満の出力ラインがあります。したがって、そのような状況では、さまざまな入力値に対して少なくとも1つの出力プロトタイプを繰り返すことができます。 3ラインから8ラインデコーダーと4ラインから16ラインデコーダーの2種類の高次デコーダーがあります。この記事では、3行から8行のデコーダーの概要について説明します。

デコーダーとは何ですか?

デコーダーは 組み合わせ論理回路 これは、コードを一連の信号に変更するために使用されます。エンコーダの逆のプロセスです。デコーダ回路は複数の入力を受け取り、複数の出力を提供します。デコーダ回路は、「n」入力のバイナリデータを「2 ^ n」固有の出力に取り込みます。入力ピンに加えて、デコーダにはイネーブルピンがあります。これにより、ピンが無効になると、回路が非アクティブになります。この記事では、3〜8行のデコーダーとデマルチプレクサーについて説明します。

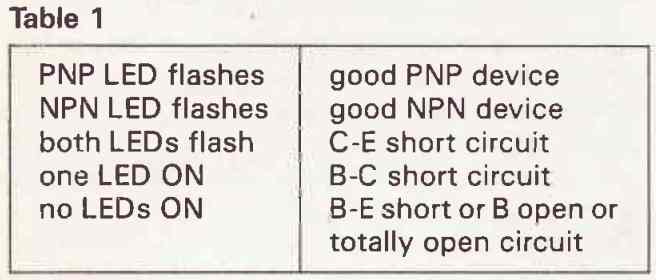

以下は、Aが入力で、D0とD1が出力である単純な1〜2ラインデコーダの真理値表です。

1〜2デコーダー

この回路は、1〜2個のデコーダロジックを示しています。

1〜2デコーダ回路

デマルチプレクサは、単一の入力を受け取り、いくつかの出力ラインの1つを提供するデバイスです。デマルチプレクサは、単一の入力データを1つ受け取り、単一の出力ラインのいずれかを一度に1つずつ選択します。それは マルチプレクサの逆プロセス 。 DEMUXまたはデータディストリビューターとも呼ばれます。 DEMUXは、入力シリアルデータラインを出力パラレルデータに変換します。 DEMUXは、単一の入力で「n」選択ラインに「2n」出力を提供します。

デマルチプレクサ

DEMUXは、回路がデータ信号を多くのデバイスの1つに送信する場合に使用されます。デコーダーは多くのデバイスから選択するために使用されますが、デマルチプレクサーは信号を多くのデバイスに送信するために使用されます。

以下は、「I」を入力データ、D0とD1を出力データライン、Aを選択ラインとする1〜2デマルチプレクサの真理値表です。

1〜2デマルチプレクサ真理値表

この回路は、1〜2デマルチプレクサの回路図を示しています。

1〜2デマルチプレクサ

なぜデコーダーが必要なのですか?

デコーダーの主な機能は、エンコーダーとは逆であるため、コードを信号のセットに変更することですが、デコーダーの設計は簡単です。デコーダーとデマルチプレクサーの主な違いは、1つの入力のみを許可し、それを出力の1つに送るために使用される組み合わせ回路です。一方、デコーダーは複数の入力を許可し、デコードされた出力を生成します。

3行から8行のデコーダーの設計手順

ここで、3ラインから8ラインのデコーダーは、2ラインから4ラインのデコーダーのような2つの低次デコーダーで設計された高次デコーダーです。このデコーダーを実装する前に、2ラインから4ラインのデコーダーを設計しました。

2行から4行のデコーダー

この2ラインから4ラインのデコーダーには、A0とA1のような2つの入力と、Y0からY4のような4つの出力が含まれています。このデコーダのブロック図を以下に示します。

2行から4行のデコーダー

入力とイネーブルが1の場合、出力は1になります。これが2〜4デコーダーの真理値表です。

IS | A1 | A0 | Y3 | Y2 | Y1 | Y0 |

0 | バツ | バツ | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

すべての出力のブール式は次のとおりです。

Y3 =E。A1。 A0

Y2 = E。 A1。 A0 '

Y1 =E。A1 '。 A0

Y0 =E。A1 '。 A0 '

このデコーダーのすべての出力には、1つの積項が含まれています。したがって、4つの積項は、各ゲートに3つの入力と2つのインバーターが含まれる4つのANDゲートを介して実装できます。 2〜4デコーダの論理図を以下に示します。したがって、このデコーダーの出力は、入力とイネーブルの最小項に他なりません。イネーブルがゼロの場合、その後、すべてのデコーダーの出力はゼロに等しくなります。同様に、3行から8行のデコーダーは、A0、A1、およびA2の3つの入力変数に対して8つの最小項を生成します。

2〜4デコーダーの論理図

3行から8行のデコーダーの実装

この3ラインから8ラインのデコーダーの実装は、2つの2ラインから4ラインのデコーダーを使用して実行できます。 2〜4ラインデコーダには2つの入力と4つの出力が含まれることを上で説明しました。したがって、3ラインから8ラインのデコーダーには、A2、A1、A0などの3つの入力と、Y7〜Y0からの8つの出力が含まれます。

次の式は、 高次デコーダーの実装 低次デコーダーの助けを借りて

必要な低次デコーダの数は m2 / m1

どこ、

低次デコーダーのo / ps数は「m1」です

高次デコーダーのo / ps数は「m2」です

たとえば、m1 = 4&m2 = 8の場合、これらの値を上記の式に代入します。必要な番号を取得できます。デコーダーの数は2です。したがって、単一の3〜8デコーダーを実装するには、2つの2ライン〜4ラインデコーダーが必要です。ここでは、2つの2〜4デコーダーを使用したブロック図を以下に示します。

2〜4ラインを使用した3〜8デコーダー

A2、A1、A0のような並列入力は、3ラインから8ラインのデコーダーに与えられます。ここでは、デコーダのピンがY7からY0のような出力を取得できるようにするために、A3の補数が与えられています。これらの出力は、8分未満です。上記のデコーダでは、ピンがY15〜Y8から出力を取得できるようにA3入力が接続されています。したがって、これらの出力は上位8分です。

論理ゲートを使用した3ラインから8ラインのデコーダ

3〜8ラインデコーダでは、3つの入力と8つの出力が含まれます。ここでは、入力はA、B、Cで表され、出力はD0、D1、D2…D7で表されます。

8つの出力の選択は、3つの入力に基づいて行うことができます。したがって、この3行から8行のデコーダーの真理値表を以下に示します。次の真理値表から、3つの選択入力に応じてDO –D7からの8つの出力のうちの1つを選択できることがわかります。

| に | B | C | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

上記の3行から8行のデコーダーの真理値表から、論理式は次のように定義できます。

D0 = A’B’C ’

D1 = A’B’C

D2 = A’BC ’

D3 = A’BC

D4 = AB’C ’

D5 = AB’C

D6 = ABC ’

D7 = ABC

上記のブール式から、3〜8個のデコーダ回路の実装は、3つのNOTゲートと8〜3つの入力ANDゲートを使用して実行できます。

上記の回路では、3つの入力を8つの出力にデコードできます。ここで、すべての出力は3つの入力変数の中間項の1つを表します。

上記の論理回路の3つのインバーターは入力の補数を提供し、ANDゲートのそれぞれが中間項の1つを生成します。

この種のデコーダーは、主に3ビットコードをデコードするために使用され、入力コードの8つの異なる組み合わせに相当する8つの出力を生成します。

このデコーダーの入力は3ビットの2進数を表し、出力は8進数システム内の8桁を表すため、このデコーダーは2進数から8進数へのデコーダーとも呼ばれます。

3ラインから8ラインのデコーダブロック図

このデコーダ回路は、3つの入力に対して8つのロジック出力を提供し、イネーブルピンを備えています。この回路は、ANDおよびNAND論理ゲートを使用して設計されています。 3つのバイナリ入力を受け取り、8つの出力の1つをアクティブにします。 3〜8ラインデコーダ回路 バイナリから8進数のデコーダーとも呼ばれます。

3〜8ラインデコーダのブロック図

デコーダ回路は、イネーブルピン(E)がハイの場合にのみ機能します。 S0、S1、およびS2は、3つの異なる入力であり、D0、D1、D2、D3です。 D4。 D5。 D6。 D7は8つの出力です。ザ・ 3〜8ラインデコーダの論理図 以下に示します。

“導体と半導体の違い ”

3〜8デコーダ回路

3〜8行デコーダーと真理値表

以下の表は、3〜8ラインデコーダの真理値表を示しています。

| S0 | S1 | S2 | IS | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| バツ | バツ | バツ | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

イネーブルピン(E)がローの場合、すべての出力ピンがローになります。

1〜8デマルチプレクサ

に 1行から8行のデマルチプレクサ 1つの入力、3つの選択入力ライン、および8つの出力ラインがあります。選択した入力に応じて、1つの入力データを8つの出力ラインに分配します。 Dinは入力データ、S0、S1、S2は選択入力、Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7は出力です。

1〜8 DEMUX

1〜8デマルチプレクサ回路の回路図を以下に示します。

1〜8デマルチプレクサ回路

3〜8デコーダ/デマルチプレクサ

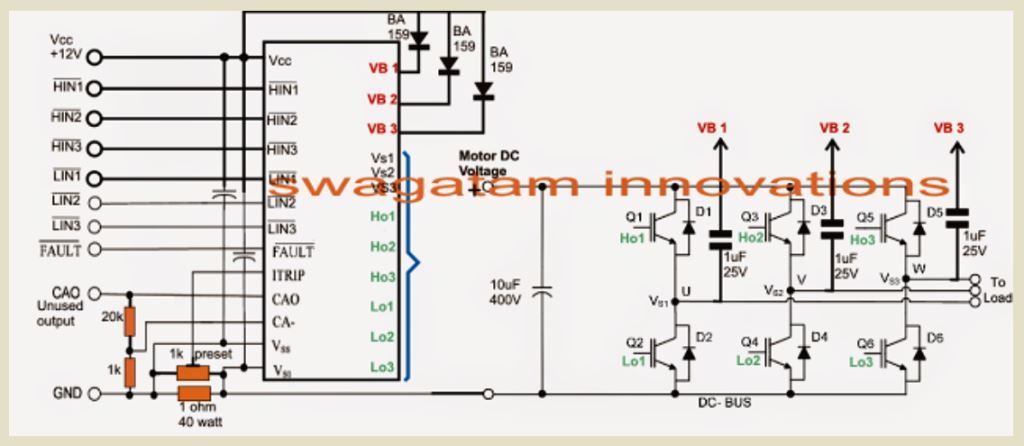

3〜8ラインデコーダIC 74HC238はデコーダー/デマルチプレクサーとして使用されます。 3〜8ラインデコーダデマルチプレクサは、デコーダとデマルチプレクサの両方として使用できる組み合わせ回路です。 IC 74HC238は、3つのバイナリアドレス入力(A0、A1、A2)を8つの出力(Y0〜Y7)にデコードします。このデバイスには、3つのイネーブルピンもあります。同じ組み合わせがデマルチプレクサとして使用されます。

ピン配置

以下は、IC74HC238 3〜8ラインデコーダまたはデマルチプレクサのピン構成です。 16ピンDIPです。

回路

論理回路はIC74HC238の動作を説明しています。

74HC238ICの特徴

- 逆多重化機能

- 複数の入力により簡単に拡張できます

- メモリチップセレクトのデコードに最適

- アクティブHIGH相互に排他的な出力

- 複数パッケージオプション

デコーダーの応用

デマルチプレクサのアプリケーション

- 単一のソースを複数の宛先に接続するために使用されます。

- Demuxは、通信システムで複数のデータ信号を単一の伝送ラインに伝送するために使用されます。

- 算術論理演算装置で使用

- データ通信のシリアルからパラレルへのコンバータで使用されます。

したがって、これは3〜8ラインデコーダーとデマルチプレクサーに関する基本情報です。デジタル論理回路と真理値表およびそれらのアプリケーションを観察することにより、このトピックに関するいくつかの基本的な概念を理解できたと思います。さらに、この記事または 最新のエレクトロニクスプロジェクト 、このトピックに関するあなたの意見は、以下のコメントセクションに書くことができます。