についての現実に入る前に エンコーダーとデコーダー 、多重化について簡潔に考えてみましょう。定期的に、いくつかの入力信号を単独の負荷に一度に供給することが期待されるアプリケーションを調べます。負荷に供給する入力信号の1つを選択するこの手順は、多重化と呼ばれます。この操作の逆、つまり、1つの共通信号ソースからいくつかの負荷に栄養を与える方法は次のとおりです。 逆多重化として知られています 。同様に、デジタルドメインでは、情報の送信を簡単にするために、情報は定期的にスクランブルされるか、コード内に設定され、その後、この保護されたコードが送信されます。コレクターでは、コード化された情報がコードからデコードまたは蓄積され、同様に表示またはロードに渡されるように処理されます。

“橋の目的は何ですか ”

2〜4ラインデコーダー

情報の暗号化とスクランブル解除のこの割り当ては、エンコーダーとデコーダーによって終了します。では、実際にエンコーダーとデコーダーとは何かを理解してみませんか。

デコーダーとは何ですか?

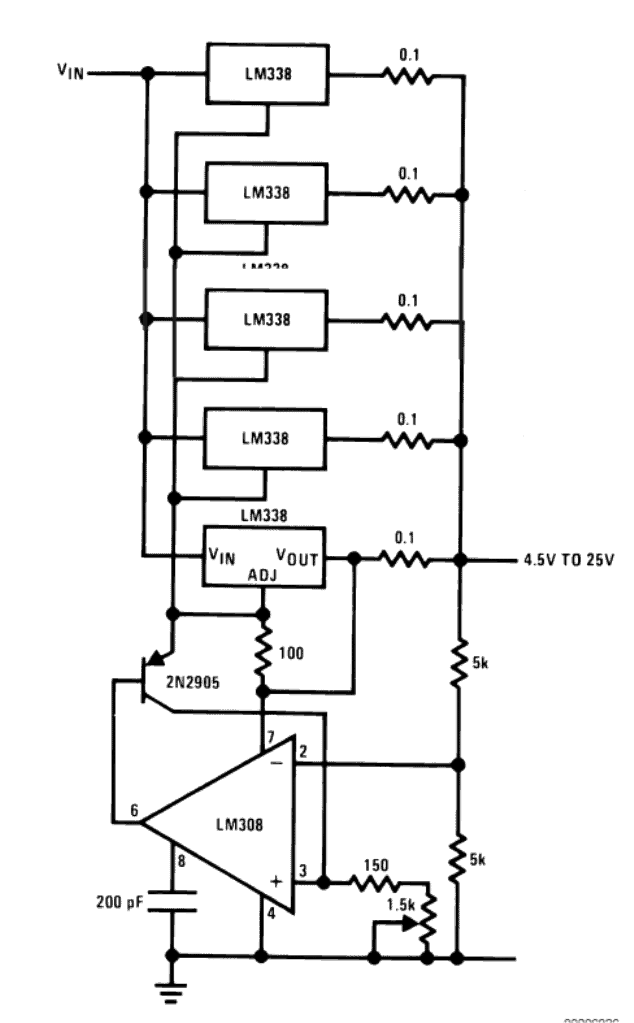

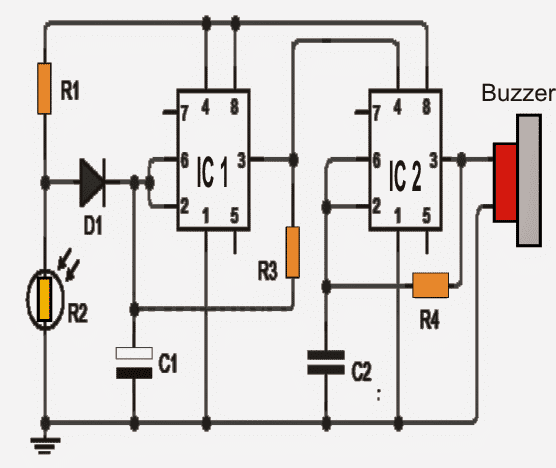

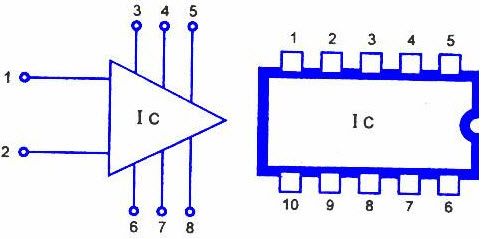

デコーダーは、コードi / psをコード化されたo / psに変更する多入力多出力論理回路であり、入力と出力の両方が、たとえばnから2nまで、および2進化10進デコーダーとは異なります。デコードは、データ多重化、メモリアドレスデコード、7セグメントディスプレイなどのアプリケーションに不可欠です。デコーダ回路の最良の例は、ANDゲートです。これは、すべての入力が「High」の場合、このゲートの出力が「High」であり、「アクティブHigh出力」と呼ばれるためです。 ANDゲートの代わりに、NANDゲートが接続されている場合、出力はすべての入力が「ハイ」の場合にのみ「ロー」(0)になります。このようなo / pは「アクティブロー出力」と呼ばれます。

デコーダ

もう少し難しいデコーダーは、nから2nタイプのバイナリデコーダーです。これらの種類のデコーダーは、バイナリ情報をnコード化された入力からほとんどの2n個の排他的出力に変更する組み合わせ回路です。そのときビットコード化されたデータにアイドルビットの組み合わせがある場合、デコーダーの出力は2n未満になる可能性があります。 2対4、 3対8ラインデコーダー または4対16デコーダーは他の例です。

並列2進数はデコーダーへの入力であり、入力での特定の2進数の発生を通知するために使用されます。出力は、デコーダー入力に正確な数が存在するかどうかを示します。

2〜4ラインデコーダ回路の設計

に似ています マルチプレクサ回路 、デコーダは特定のアドレスラインに制限されていないため、3つ以上の出力(2つ、3つ、または4つのアドレスライン)を持つことができます。デコーダ回路は、2、3、または4ビットの2進数をデコードするか、最大4、8、または16の時分割多重信号をデコードできます。

2対4デコーダ回路

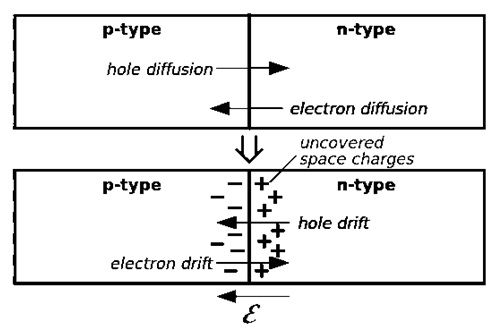

“導体半導体と絶縁体の違い ”

デコーダーとして、この回路はnビットの2進数を取り、2n個の出力ラインの1つに出力を生成します。したがって、通常、アドレス指定i / pラインの数とデータo / pラインの数で表されます。一般的なデコーダICには、2つの2〜4ライン回路、3〜8ライン回路、または 4-16ラインデコーダー 回路。この回路のバイナリ特性の1つの除外は、4〜10行デコーダです。これは、2進化10進(BCD)入力を0〜9の範囲の出力に変更するために提案されています。

この回路をデコーダーとして使用する場合は、o / psにデータラッチを挿入して、他の信号が伝送されている間、すべての信号を保持することができます。ただし、この回路をデコーダーとして使用している場合、これは関係ありません。その場合、1つのアクティブなo / pだけを入力コードと等しくする必要があります。

2〜4行デコーダの真理値表

このタイプのデコーダーでは、デコーダーには2つの入力、つまりA0、A1、およびD0、D1、D2、およびD3で示される4つの出力があります。次の真理値表でわかるように、入力の組み合わせごとに、1つのo / p行がオンになります。

2対4デコーダの真理値表

上記の例では、デコーダーの各o / pが真に最小項であり、入力の組み合わせが保証されているため、次のようになっていることがわかります。

D0 = A1 A0、(minterm m0)入力00に対応D1 = A1 A0、(minterm m1)入力01に対応D2 = A1 A0、(minterm m2)入力10に対応D3 = A1 A0、(minterm m3 )これは入力11に対応します

ザ・ 回路はANDゲートで実装されています 、図に示すように。この回路では、D0の論理式はA1 / A0などです。したがって、デコーダーの各出力は、入力の組み合わせに対して生成されます。

デコーダーのアプリケーション

デコーダーのアプリケーションは、 さまざまな電子プロジェクトの作成 。

- ウォーフィールド-ナイトビジョンフライングカメラを備えたフライングロボット

- 金属探知機付きロボット車両

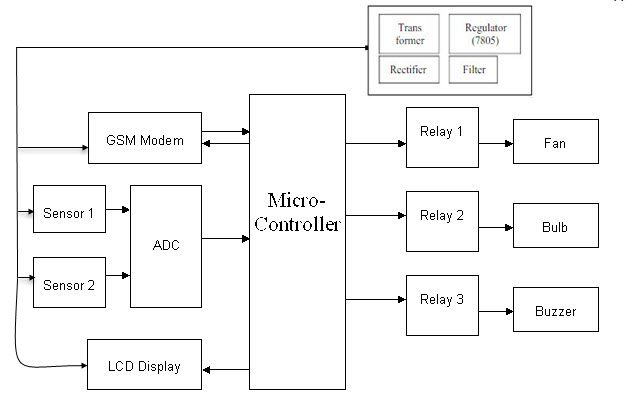

- RFベースのホームオートメーションシステム

- 産業における複数のモーターの速度同期

- 患者のための病院の自動無線健康監視システム

- シークレットコードにより、RFテクノロジーを使用した安全な通信が可能

これはすべてデコーダーとそのアプリケーションに関するものです コミュニケーションベースのプロジェクト 。私たちは、あなたがこの概念についてより良い考えを持っているかもしれないと信じています。さらに、この記事に関する疑問がある場合は、以下のコメントセクションにコメントして、貴重な提案をしてください。