この投稿は、コンパレータICデータシートに一般的に見られる重要なコンパレータパラメータまたは仕様のいくつかを理解するのに役立ちます。

コンパートメントのデータシートで遭遇する可能性のある主なパラメータのいくつかは次のとおりです。

- 伝播遅延

- 消費電流

- 出力段タイプ(オープンコレクタ/ドレインまたはプッシュプル)

- 入力オフセット電圧、ヒステリシス

- 出力電流能力

- 立ち上がり時間と立ち下がり時間

- 入力同相電圧範囲

これらとは別に、入力バイアス電流、コモンモードと電源除去比、サンプル/ホールド機能、起動時間などの他のパラメータもあります。

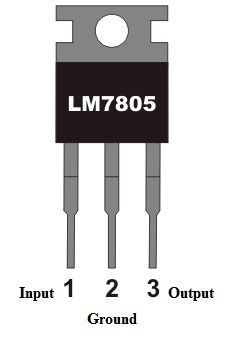

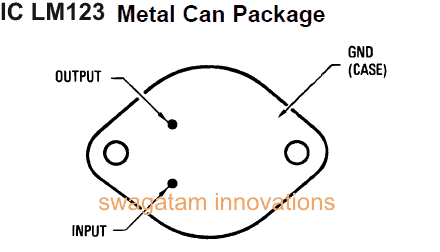

ほとんどの場合、1つのコンパレータチップには5つのピンがあります。電源入力VCC +、VCC-用の2つのピン、入力信号IN +、IN-を供給するための2つのピン、および1つの出力OUTピンです。一部のICでは、スタンバイ機能用に追加のピンがある場合があります。

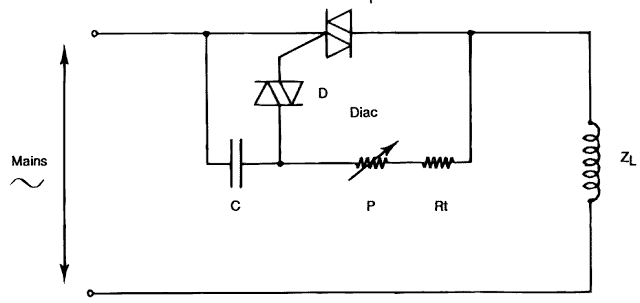

私たちから 以前の議論 VIN(+)> VIN(-)の場合、VIN(+)の場合、出力はハイ状態になります。 言い換えると、非反転入力(+)の電圧レベルが反転入力(-)よりも高い場合、コンパートメント内の出力トランジスタはオフになります。 そのコレクターピンが開いた状態を示すことを意味します。このコレクタピンはプルアップ抵抗を介して正の電源レールにリンクされることになっているため、この状況でコレクタが正または高論理出力を持つことができます。 出力ピンの構成に関しては、コンパレータにはプッシュプルとオープンコレクタ(オープンドレイン)の2種類があります。 プッシュプル構成では、負荷をコンパートメントのコレクタピンと正のラインの間に直接接続して、入力信号の状態に応じて負荷のオン/オフを切り替えることができます。これはプッシュプルスイッチングのように機能するため、この名前が付けられています。 あるいは、コレクタピンをプルアップ抵抗を介して正のレールに接続し、コレクタ出力をプッシュプルロジック出力として使用することもできます。この構成の利点の1つは、コンパレータのVccとは異なる電圧レベルを負荷に使用できることです。 オープンコレクタモードでは、コンパレータは電流をシンクすることしかできず、負荷に電流を供給することはできません。スコープが限られているため、このモードが使用されることはめったにありませんが、指定されたアプリケーションのORゲートモードで複数の出力を接続できます。 入力コモンモード電圧範囲は、コンパートメントの許容入力範囲内に入る電圧の尺度です。 これは、コンパートメントの両方の入力が構成の機能を保証するために強制的に使用される電圧範囲です。 このモードでは、入力は入力ピン全体でVcc〜0Vの完全な電源範囲で動作するため、レールツーレール入力段とも呼ばれます。 ただし、デバイスの消費電力を最小限に抑えるために、必要な場合を除いて、レールツーレールのコモンモード入力範囲を避けることをお勧めします。 VIOパラメータは、出力の状態を切り替える寸前の最小入力差値です。入力での入力オフセット電圧の差動レベルは、コンパレータの分解能に影響を与える可能性があります。これは、この差動の大きさが非常に小さく、出力トグル状態が不安定になる可能性があるためです。したがって、このような小さなオフセット信号は、出力が異常に動作するか、まったく切り替わらない原因となる可能性があります。 差動が低いと、コンパレータトランジスタが不安定になり、入力オフセット電圧条件が増加する可能性があります。 内部を持っているコンパートメントのために ヒステリシス 有効VIOは、VTRIP +とVTRIP-の合計の平均レベルとして定義され、VHYST = VTRIP + -VTRIP-のヒステリシス値です。ここで、VTRIP +とVTRIP-は、出力をロー状態からハイ状態に切り替える入力差動電圧を構成します。またはそれぞれ高から低の状態。 CMRRは、同相信号除去比の略で、入力オフセット電圧VIOと入力同相電圧VICMの関係を示します。これは、入力オフセット電圧に対するコモンモード電圧値の比率として理解できます。このパラメータは通常、対数目盛で次のように表されます。 CMRR [dB] = 20•log(|ΔVICM/ΔVIO|) CMRRは、2つの異なる入力コモンモード電圧(通常は0 VとVCC)に対して取得された2つの入力オフセット電圧の大きさを測定することによって計算されます。 SVRという用語は「電源電圧除去」の略で、入力オフセット電圧VIOと電源電圧の関係を提供するパラメータとして定義されます。 電源電圧を変更すると、入力差動トランジスタペアのバイアスにいくらか影響を与える可能性があります。これは、変動によって入力オフセット電圧もわずかに変化する可能性があることを意味します。 これは次の式で表されます。 SVR [dB] = 20•log(|ΔVCC/ΔVIO|) このパラメータは、コンパレータの正味ゲインを理解するのに役立ちます。コンパレータがより高いゲイン仕様に起因する場合、それは小さな入力信号の差に対するデバイスの応答が改善されることを意味します。 通常、コンパートメントのAVD範囲は200V / mV(106dB)です。理論的には、1mVの入力を106dBで増幅すると、200Vの振幅が達成されます。ただし、実際のデバイスの場合、ピークレベルの振幅はVccの値によって制限されます。 AVDは、出力が高状態または低状態のいずれかになり、その間にあることはないため、外部ヒステリシスに影響を与えることはないことに注意してください。 TPDは、入力信号が基準入力レベルをちょうど超えた瞬間と、出力状態がちょうど変化した瞬間との間の時間差として定義されます。 以前の説明から、コンパートメントの出力は入力ピンの電圧差に応答してトグルすることがわかります。 伝搬遅延TPDは、入力ピンが差を感知して出力を問題なく切り替えることができる速度を示す仕様を提供します。 基本的に、TPDは、コンパレータが有効な出力応答を生成するために快適に処理できる入力周波数レベルについて教えてくれます。 ヒステリシスは、不安定な入力や変動する入力に応じて出力をすばやく変更することを禁止するパラメータであることがわかっています。 通常、コンパレータでは、入力差動信号が基準値に近づくと、出力電圧が急速に振動または変動する可能性があります。または、これは、入力信号の振幅が非常に小さく、入力差動レベルが速い速度で変化する場合に発生する可能性があります。 実際には、ヒステリシス機能が組み込まれている多くのコンパレータデバイスがあります。これは数mV前後である可能性があり、デバイスの解像度に影響を与えることなく、不要な出力スイッチングを抑制するのに十分です。 このようなデバイスの場合、評価された平均上限電圧と下限電圧は入力オフセット電圧VIOと呼ばれ、VTRIP + / VTRIP-の差はヒステリシス電圧またはVHYSTと呼ばれます。 コンパレータにヒステリシスが組み込まれていない場合、または目的のヒステリシスレベルが比較的大きい場合は、以下に示すように、正のフィードバックネットワークを介してヒステリシス機能を実装するための外部構成を追加できます。 まとめ したがって、これらのいくつかの重要なコンパレータデータシートパラメータは、完全なコンパレータベースの設計を達成しようとしているすべての愛好家に役立ちます。 さらに詳しい情報 このテーマに関しては、コメントを通じてお気軽に共有してください。出力段タイプ(オープンコレクタ/ドレインまたはプッシュプル)

コンパレータデータシートパラメータ

入力同相電圧範囲-VICM:

入力オフセット電圧-VIO(VTRIP)

CMRRとSVR

電圧利得

伝播遅延

ヒステリシス

内蔵ヒステリシス

外部ヒステリシス

前:神の偶像のための回転LEDチャクラ回路 次へ:水晶発振器回路を理解する